4 Analog-to-Digital Conversion

4.1 Flash Analog-to-Digital Converter

Flash Analog-to-Digital Converters are used

for systems that need the highest speeds available. Some applications of

flash ADC include radar, high speed test equipment, medical imaging and

digital communication. The difference with this and other types of

ADC is that the input signals are processed in a parallel method.

Flash converters operate by simultaneously comparing the input signal with

unique reference levels spaced 1 least significant bit apart. This

requires many front-end comparators and a large digital encoding section.

Simultaneously, each comparator generates an output to a priority encoder

which then produces the digital representation of the input signal level.

In order for this to work you have to use one comparator for each least

significant bit. Therefore, a 8-bit flash converter requires 255 comparators

along with high speed logic to encode the comparator outputs.

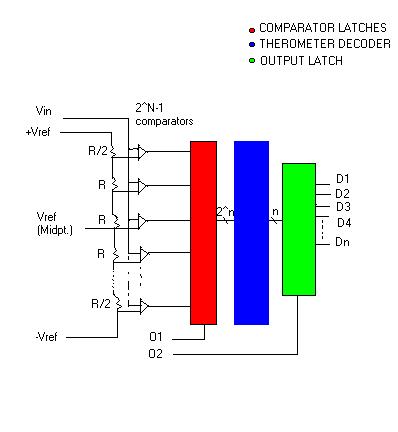

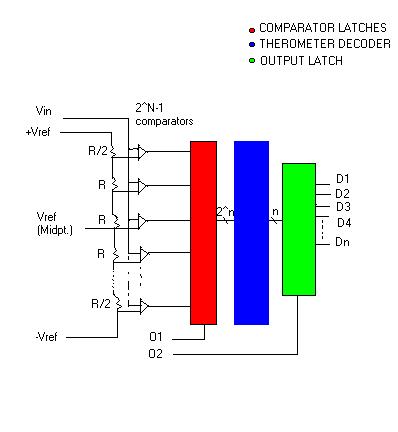

BASIC ARCHITECTURE OF A FLASH A/D CONVERTER.

In the diagram, note that input signal is simultaneously

measured by each comparator which has a unique resistor ladder generated reference.

This produces a series of 1s and 0s such that the outputs will be all 1s when

below the reference levels. The comparator output is called a thermometer.

Following the comparator outputs is the digital section consisting of several

logic gates for encoding the thermo codes. The thermometer decoder determines

the point where the series of 1s and 0s form a boundary. The priority

encoder encoder uses this boundary threshold for conversion to binary output.

Output from the priority encoder are then available to the system memory.

It is important that the memory system be designed properly to prevent lost

data since every new conversion will overwrite the previous result.

CMOS Flash ADC

There are two types of Flash ADC where one is

bipolar and the other is CMOS. The difference is in how the front

end of the comparators are created. CMOS is used for the ease of

using analog switches and capacitors. CMOS flash converters can equal

the speed of all except the bipolar designs with emitter-coupled logic.

The advantage of using CMOS is that the power consumption is less with

the N and P channels.

Bipolar Flash ADC

Using Bipolar components gives a different frequency

response limitation due to the transistors. Buffers are used to prevent

the input and reference signal from excessive comparator loading. These

buffers responsible for the dynamic performance of ADC. Although it

is possible to use TTL or CMOS, ECL (emitter-coupled logic) is used for the

highest speed. The high speed is possible by using ECL for the encoding

stage which requires a negative supply voltage. This means that the

bipolar comparators also need a negative supply voltage. ECL is faster

because is keeps the logic transistors from operation in the saturated state

(restricted to either cutoff or active). This eliminates the charge

storage delays that occur when a transistor is driven in the saturated mode.

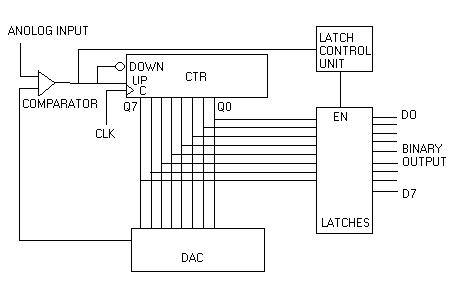

4.2 Tracking Analog-to-Digital Converter

Tracking uses an up down counter and is faster that the digital ramp

single or multi-slope ADC because the counter is not reset after each sample.

It tracks analog input hence the name tracking. In order for this to work,

the output reference voltage should be lower than the analog input. When

the comparator output is high, the counter is in counting up mode of binary

numbers. As a result, this increases stair step reference voltage out

until the ramp reaches the input voltage amount. When reference voltage

equals the input voltage the comparators output is switched to low mode and

starts counting down. If the analog input is decreasing the counter will

continue to back down to track input. If the analog input is increasing the

counter will go down one count and resume counting up to follow the curve or

until the comparison occurs.

An 8 - bit tracking ADC

4.3 Single-Slope Analog-to-Digital Converter

Single-slope ADCs are appropriate for very high accuracy of

high-resolution measurements where the input signal bandwidth is relatively

low. Besides the accuracy these types of converters offer a low-cost

alternative to others such as the successive-approximation approach.

Typical applications for these are digital voltmeters, weighing scales,

and process control. They are also found in battery-powered instrumentation

due to the capability for very low power consumption.

The name implies that single-slope ADC use only one ramp cycle to measure

each input signal. The single-scope ADC can be used for up to 14-bit

accuracy. The reason for only 14-bit accuracy is because single-slope ADC

is more susceptible to noise. Because this converter uses a fixed

ramp for comparing the input signal, any noise present at the comparator

input while the ramp is near the threshold crossing can cause errors.

The basic idea behind the single slope converter is to time how long it takes

for a ramp to equal an input signal at a comparator. Absolute measurements

require that an accurate reference (Vref) matching the desired accuracy be

used for comparing the time with the unknown input measurement. Therefore

the input unknown (Vun) can be determined by:

Vun = Vref(Tun/Tref)

Where the ratio is directly proportional to the difference in magnitudes.

The main part of the single-slope analog to digital converter is the ramp

voltage required to compare with the input signal. If the ramp function

is highly linear then the system errors will be completely canceled.

Since each input is measured with the same ramp signal and hardware, the component

tolerances are exactly the same for each measurement. Regardless of the initial

conditions or temperature drifts, no calibration or auto zero function is

required

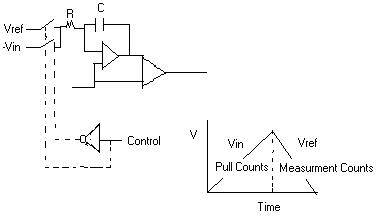

4.4 Dual-Slope Analog-to-Digital Converter

Dual-Slope ADC operate on the principle of integrating the unknown

input and then comparing the integration times with a reference cycle.

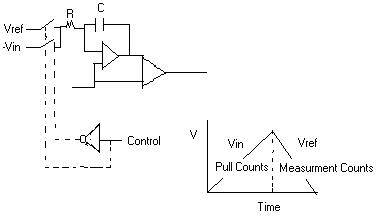

The basic way is to use two slopes (dual) as in this diagram:

This circuit operates by switching in the unknown input signal and then integrating

for full scale number counts. During this cycle the reference is switched

in and if the reference is of opposite polarity, the ramp will be driven back

towards ground. The time that is takes for the ramp to again reach

the comparator threshold of ground will be directly proportional to the unknown

input signal. Since the circuit uses the same time constant for the

integrator, the component tolerances will be the same for both the integration

and differentiation cycles. Therefore the errors will cancel except

for the offset voltage that will be additive during both the cycles.

The main benefits of this type is the increased range, the increased accuracy

and resolution, and the increased speed.

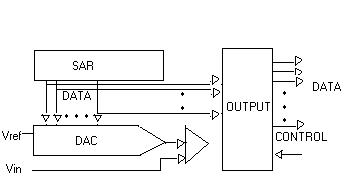

4.5 Successive-Approximation Analog-to-Digital Converter

The successive-approximation ADC is also called a sampling ADC.

The term successive-approximation comes from testing each bit of resolution

from the most significant bit to the lowest. These are the most popular

today because there is a wide range in performances and levels of integration

to fit a different amount of task. Newer successive-approximation converters

only sample the input once per conversion, whereas the earlier ones sampled

as many times as the number of bits. Sampled converters have the

advantage over the ones that don't sample because they can tolerate input signals

changing between bit tests. Non-sampled converters performance would be

downgraded if the input only changed more than a 1/2 of a least significant

bit. This is due to the inputs being sampled n times for every conversion,

where n is the bits of resolution.

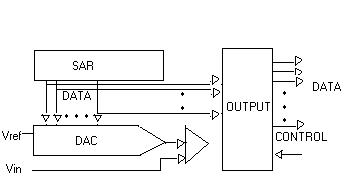

The basic principle behind this device is to use a DAC approximation of the

input and make a comparison with the input for each bit of resolution. The

most significant bit is tested first generating 1/2 Vref with the DAC and

comparing it to the sampled input signal. The successive-approximation register

(SAR) drives the DAC to produce estimates of the input signal and continuing

this process to the least significant bit. Each estimation more accurately

closes in on the input level. For each bit test, the comparator output

will determine if the estimate should stay as a 1 or 0 in the result register.

If the comparator indicates that the estimated value is under the input level,

then the bit stays set. Otherwise, the bit is reset in the result register.

An example of successive-approximation (sampling) ADC:

CONTENTS | PREV

| NEXT