# Electronics Logic Family Characteristics: Voltage

Terry Sturtevant

Wilfrid Laurier University

May 23, 2018

イロト イヨト イヨト イヨト

# Ideal logic gates

・ロト ・回 ト ・ ヨト ・ ヨト …

#### Ideal logic gates

• In PC/CP220, logic gates are treated as "ideal" devices.

イロト イヨト イヨト

#### Ideal logic gates

In PC/CP220, logic gates are treated as "ideal" devices.

As well, only one or perhaps two logic families were discussed.

# Ideal logic gates

- In PC/CP220, logic gates are treated as "ideal" devices.

As well, only one or perhaps two logic families were discussed.

- Now the real (i.e. non-ideal) operating characteristics of different logic families will be studied.

# Ideal logic gates

- In PC/CP220, logic gates are treated as "ideal" devices.

As well, only one or perhaps two logic families were discussed.

- Now the real (i.e. non-ideal) operating characteristics of different logic families will be studied.

- The operation of an *ideal* logic gate can be summarized by the following rules:

Input and output voltages will be at either the *high* or the *low* value specified for that family; (eg. 5 and 0 volts, respectively for TTL)

イロト イボト イヨト イヨト

- Input and output voltages will be at either the *high* or the *low* value specified for that family; (eg. 5 and 0 volts, respectively for TTL)

- Inputs will draw no current from whatever drives them, and outputs can supply as much current as necessary for whatever follows.

イロト イポト イヨト イヨト 三日

- Input and output voltages will be at either the *high* or the *low* value specified for that family; (eg. 5 and 0 volts, respectively for TTL)

- Inputs will draw no current from whatever drives them, and outputs can supply as much current as necessary for whatever follows.

- Any change of an input will immediately be reflected on the output.

イロト イポト イヨト イヨト 三日

Reading Data sheets

# Real logic gates

Terry Sturtevant Electronics Logic Family Characteristics: Voltage

・ロト ・回 ト ・ ヨト ・ ヨト …

Reading Data sheets

### Real logic gates

In practice, these rules do not hold.

Terry Sturtevant Electronics Logic Family Characteristics: Voltage

Reading Data sheets

#### Real logic gates

In practice, these rules do not hold.

A real logic gate operates under the following restrictions:

イロト イポト イヨト イヨト

Reading Data sheets

#### • Input voltages will not always be at ideal values

ヘロト ヘヨト ヘヨト ヘヨト

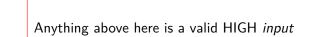

• Input voltages will not always be at ideal values a *range* of input values must be considered *high*

Input voltages will not always be at ideal values

*range* of input values must be considered *high* another range of input values must be considered *low*.

- Input voltages will not always be at ideal values a *range* of input values must be considered *high* another range of input values must be considered *low*.

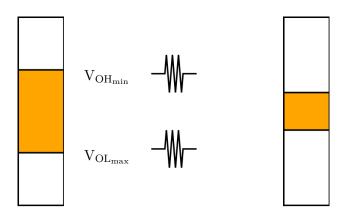

- Similarly output voltages will not always be at ideal values

イロト イボト イヨト イヨト

- Input voltages will not always be at ideal values

*range* of input values must be considered *high* another range of input values must be considered *low*.

- Similarly output voltages will not always be at ideal values a *range* of output voltages should be considered as *high*

- Input voltages will not always be at ideal values

*range* of input values must be considered *high* another range of input values must be considered *low*.

- Similarly output voltages will not always be at ideal values a range of output voltages should be considered as high another range of output voltages should be considered low.

- Input voltages will not always be at ideal values

*range* of input values must be considered *high* another range of input values must be considered *low*.

- Similarly output voltages will not always be at ideal values a *range* of output voltages should be considered as *high* another *range* of output voltages should be considered *low*.

- Changes made at the inputs will take a finite amount of time to be reflected on the outputs.

イロト イヨト イヨト

- Input voltages will not always be at ideal values

*range* of input values must be considered *high* another range of input values must be considered *low*.

- Similarly output voltages will not always be at ideal values a *range* of output voltages should be considered as *high* another *range* of output voltages should be considered *low*.

- Changes made at the inputs will take a finite amount of time to be reflected on the outputs.

- Inputs must draw a small but finite amount of current from whatever is driving them in order that they will be recognized.

イロト 不得 トイヨト イヨト 二日

- Input voltages will not always be at ideal values

*range* of input values must be considered *high* another range of input values must be considered *low*.

- Similarly output voltages will not always be at ideal values a *range* of output voltages should be considered as *high* another *range* of output voltages should be considered *low*.

- Changes made at the inputs will take a finite amount of time to be reflected on the outputs.

- Inputs must draw a small but finite amount of current from whatever is driving them in order that they will be recognized.

- Outputs have a limited current capacity for maintaining the output voltage at the desired level.

イロト 不得 トイヨト イヨト 二日

Reading Data sheets

# Real logic gates

Terry Sturtevant Electronics Logic Family Characteristics: Voltage

・ロト ・回 ト ・ ヨト ・ ヨト …

Reading Data sheets

#### Real logic gates

Terry Sturtevant Electronics Logic Family Characteristics: Voltage

Reading Data sheets

#### Real logic gates

Terry Sturtevant Electronics Logic Family Characteristics: Voltage

문 🛌 문

Reading Data sheets

### Real logic gates

Terry Sturtevant Electronics Logic Family Characteristics: Voltage

Reading Data sheets

#### Real logic gates

Terry Sturtevant Electronics Logic Family Characteristics: Voltage

Reading Data sheets

#### Real logic gates

Terry Sturtevant Electronics Logic Family Characteristics: Voltage

Reading Data sheets

#### Real logic gates

Terry Sturtevant Electronics Logic Family Characteristics: Voltage

Reading Data sheets

### Real logic gates

Terry Sturtevant Electronics Logic Family Characteristics: Voltage

Reading Data sheets

### Real logic gates

Terry Sturtevant Electronics Logic Family Characteristics: Voltage

문 🛌 문

Reading Data sheets

### Real logic gates

Terry Sturtevant Electronics Logic Family Characteristics: Voltage

문 🛌 문

Reading Data sheets

#### Real logic gates

Terry Sturtevant Electronics Logic Family Characteristics: Voltage

Reading Data sheets

#### Real logic gates

Terry Sturtevant Electronics Logic Family Characteristics: Voltage

문 🛌 문

Reading Data sheets

#### Real logic gates

Terry Sturtevant Electronics Logic Family Characteristics: Voltage

문 🛌 문

Reading Data sheets

#### Real logic gates

Terry Sturtevant Electronics Logic Family Characteristics: Voltage

Reading Data sheets

#### Real logic gates

Terry Sturtevant Electronics Logic Family Characteristics: Voltage

Reading Data sheets

### Real logic gates

Terry Sturtevant Electronics Logic Family Characteristics: Voltage

Reading Data sheets

## Real logic gates

Terry Sturtevant Electronics Logic Family Characteristics: Voltage

문 🛌 문

Reading Data sheets

#### More detail

Terry Sturtevant Electronics Logic Family Characteristics: Voltage

Reading Data sheets

#### More detail

Terry Sturtevant Electronics Logic Family Characteristics: Voltage

Reading Data sheets

#### More detail

Terry Sturtevant Electronics Logic Family Characteristics: Voltage

Reading Data sheets

#### More detail

Terry Sturtevant Electronics Logic Family Characteristics: Voltage

Reading Data sheets

#### More detail

Terry Sturtevant Electronics Logic Family Characteristics: Voltage

Reading Data sheets

#### More detail

Terry Sturtevant Electronics Logic Family Characteristics: Voltage

Reading Data sheets

## More detail

Terry Sturtevant Electronics Logic Family Characteristics: Voltage

Reading Data sheets

#### Reading Data sheets

Terry Sturtevant Electronics Logic Family Characteristics: Voltage

ヘロト 人間 とくほ とくほ とう

2

Reading Data sheets

#### Reading Data sheets

The actual limits on voltage, current, timing, etc. will be given in manufacturer's **data sheets**.

イロト イヨト イヨト

Reading Data sheets

## Reading Data sheets

The actual limits on voltage, current, timing, etc. will be given in manufacturer's **data sheets**.

Different manufacturers arrange their data sheets differently, and use different names.

イロト イヨト イヨト

3

| Ideal logic gates<br>Real logic gates<br>Logic families | Voltage Limits<br>Noise Immunity<br>3.3V Logic<br>3.3V outputs into 5V inputs<br>5V tolerant inputs<br>5V INtolerant inputs |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

|                                                         |                                                                                                                             |

## Logic families

< ロ > < 回 > < 回 > < 回 > < 回 >

æ

Voltage Limits Noise Immunity 3.3V Logic 3.3V outputs into 5V inputs 5V tolerant inputs 5V INtolerant inputs

# Logic families

• The real limitations on *voltages*, *timing*, and *currents* depend on the *logic family* involved.

Voltage Limits Noise Immunity 3.3V Logic 3.3V outputs into 5V inputs 5V tolerant inputs 5V INtolerant inputs

# Logic families

• The real limitations on *voltages*, *timing*, and *currents* depend on the *logic family* involved.

Note that usually comparing "real" to "ideal" values involves seeing how close one number, (the "real" value) is to another (the "ideal" value).

< ロ > < 同 > < 三 > < 三 >

Voltage Limits Noise Immunity 3.3V Logic 3.3V outputs into 5V inputs 5V tolerant inputs 5V INtolerant inputs

# Logic families

• The real limitations on *voltages*, *timing*, and *currents* depend on the *logic family* involved.

Note that usually comparing "real" to "ideal" values involves seeing how close one number, (the "real" value) is to another (the "ideal" value).

• With digital logic chips, however, rather than having a single "ideal" value for a parameter, the manufacturers give **bounds** for it instead.

<ロト < 同ト < ヨト < ヨト

Voltage Limits Noise Immunity 3.3V Logic 3.3V outputs into 5V inputs 5V tolerant inputs 5V INtolerant inputs

# Logic families

• The real limitations on *voltages*, *timing*, and *currents* depend on the *logic family* involved.

Note that usually comparing "real" to "ideal" values involves seeing how close one number, (the "real" value) is to another (the "ideal" value).

• With digital logic chips, however, rather than having a single "ideal" value for a parameter, the manufacturers give **bounds** for it instead.

This is because these **specifications** are not values that should be matched, but rather they are values that should be considered as limits that one should achieve even in the "worst case" during real operation.

< ロ > < 同 > < 三 > < 三 >

| Voltage Limits<br>Noise Immunity<br>3.3V Logic<br>3.3V outputs into 5V inputs<br>5V tolerant inputs<br>5V INtolerant inputs |

|-----------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                             |

• For instance, if a family has a nominal input "high" voltage of 5 volts, then any voltage above some voltage will be considered "high".

< 回 > < 回 > < 回 >

| Ideal logic gates<br>Real logic gates<br>Logic families | Voltage Limits<br>Noise Immunity<br>3.3V Logic<br>3.3V outputs into 5V inputs<br>5V Volerant inputs<br>5V INtolerant inputs |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

|                                                         | 5V INtolerant inputs                                                                                                        |

|                                                         |                                                                                                                             |

• For instance, if a family has a nominal input "high" voltage of 5 volts, then any voltage above some voltage will be considered "high".

If an actual gate accepts a slightly lower voltage as a high, then that is not surprising and in fact is desirable.

< 回 > < 回 > < 回 >

| Ideal logic gates<br>Real logic gates<br>Logic families | Voltage Limits<br>Noise Immunity<br>3.3V Logic<br>3.3V outputs into 5V inputs<br>5V tolerant inputs<br>5V INtolerant inputs |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

|                                                         |                                                                                                                             |

Note that for some parameters the specifications will give an *upper* bound while for some they will give a *lower* bound.

| Ideal logic gates<br>Real logic gates<br>Logic families | Voltage Limits<br>Noise Immunity<br>3.3V Logic<br>3.3V outputs into 5V inputs<br>5V tolerant inputs<br>5V INtolerant inputs |  |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|

|                                                         |                                                                                                                             |  |

Note that for some parameters the specifications will give an *upper* bound while for some they will give a *lower* bound. Which one is given will make sense if you understand what each parameter means.

・ 戸 ト ・ ヨ ト ・ ヨ ト

Voltage Limits Noise Immunity 3.3V Logic 3.3V outputs into 5V inputs 5V tolerant inputs 5V INtolerant inputs

#### Supply voltage Designations

イロト イボト イヨト イヨト

Voltage Limits Noise Immunity 3.3V Logic 3.3V outputs into 5V inputs 5V tolerant inputs 5V INtolerant inputs

## Supply voltage Designations

• The supply voltages for various families have names which are based on the type of transistors used in their construction.

イロト イボト イヨト イヨト

Voltage Limits Noise Immunity 3.3V Logic 3.3V outputs into 5V inputs 5V tolerant inputs 5V INtolerant inputs

## Supply voltage Designations

• The supply voltages for various families have names which are based on the type of transistors used in their construction. For instance, TTL gates are made with **bipolar** transistors, which have a collector and an emitter, the supply voltages are  $V_{\rm CC}$  and GROUND is occasionally given as  $V_{\rm EE}$ .

< ロ > < 同 > < 三 > < 三 > 、

Voltage Limits Noise Immunity 3.3V Logic 3.3V outputs into 5V inputs 5V tolerant inputs 5V INtolerant inputs

# Supply voltage Designations

• The supply voltages for various families have names which are based on the type of transistors used in their construction.

For instance, TTL gates are made with **bipolar** transistors, which have a  ${\bf c}$ ollector and an  ${\bf e}$ mitter,

the supply voltages are  $V_{\rm CC}$  and GROUND is occasionally given as  $V_{\rm EE}.$

• On the other hand, CMOS gates are built with **field-effect** transistors which have a **d**rain and a **s**ource,

the supply voltages are  $\mathrm{V}_{\mathrm{DD}}$  and  $\mathrm{V}_{\mathrm{SS}}.$

#### Voltage Limits

Noise Immunity 3.3V Logic 3.3V outputs into 5V inputs 5V tolerant inputs 5V INtolerant inputs

## TTL Voltage Limits

Terry Sturtevant Electronics Logic Family Characteristics: Voltage

・ロト ・回ト ・ヨト ・ヨト

æ

Voltage Limits Noise Immunity 3.3V Logic 3.3V outputs into 5V input 5V tolerant inputs 5V INtolerant inputs

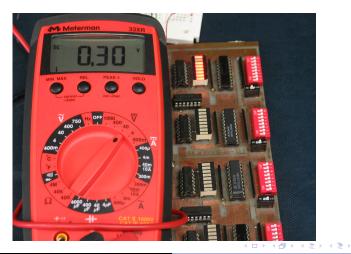

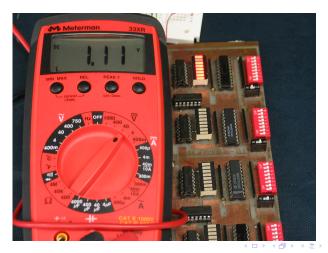

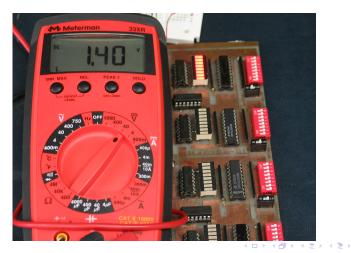

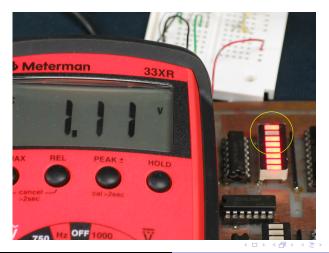

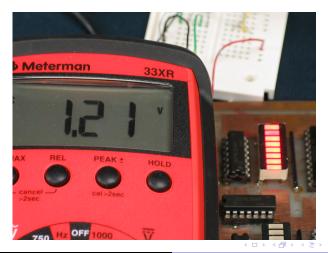

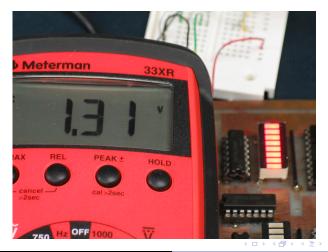

# TTL Voltage Limits

While the *ideal* voltage in TTL circuits are 0 (logic 0) and +5 volts (logic 1), the typical, or observed, voltages are different in practice.

イロト イボト イヨト イヨト

Voltage Limits Noise Immunity 3.3V Logic Logic families SV tolerant inputs

# TTL Voltage Limits

While the *ideal* voltage in TTL circuits are 0 (logic 0) and +5 volts (logic 1), the typical, or observed, voltages are different in practice. It is important to know what **tolerances** must be observed in order to guarantee the correct operation of a digital circuit.

イロト イポト イヨト イヨト

Voltage Limits

Ideal logic gates

Noise Immunity

Real logic gates

3.3V Logic

Logic families

3.3V outputs into 5V inputs

5V tolerant inputs

5V INtolerant inputs

# TTL Voltage Limits

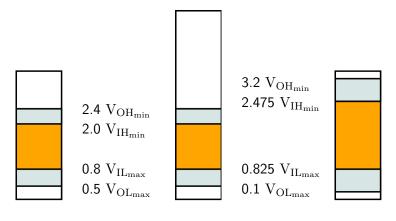

While the *ideal* voltage in TTL circuits are 0 (logic 0) and +5 volts (logic 1), the typical, or observed, voltages are different in practice. It is important to know what **tolerances** must be observed in order to guarantee the correct operation of a digital circuit. Four particular quantities are of interest in specifying the tolerance:

< ロ > < 同 > < 回 > < 回 > .

#### Voltage Limits

Noise Immunity 3.3V Logic 3.3V outputs into 5V inputs 5V tolerant inputs 5V INtolerant inputs

<ロ> <同> <同> < 同> < 同> < 三> < 三> 三三

#### Voltage Limits

Noise Immunity 3.3V Logic 3.3V outputs into 5V inputs 5V tolerant inputs 5V INtolerant inputs

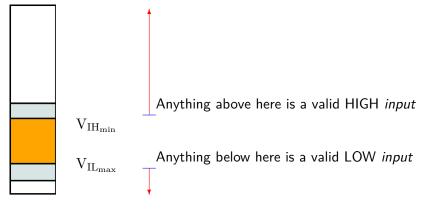

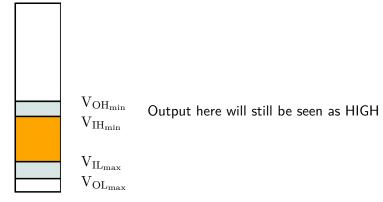

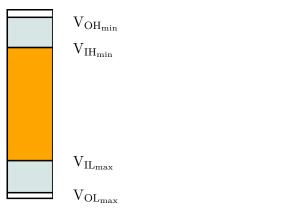

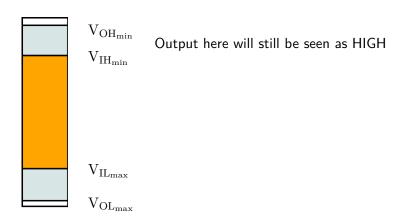

## $\bullet \ V_{IH_{\min}}$

the *minimum* input voltage which will be accepted as a logic 1.

#### Voltage Limits

Noise Immunity 3.3V Logic 3.3V outputs into 5V inputs 5V tolerant inputs 5V INtolerant inputs

## $\bullet \ V_{IH_{min}}$

the *minimum* input voltage which will be accepted as a logic 1.

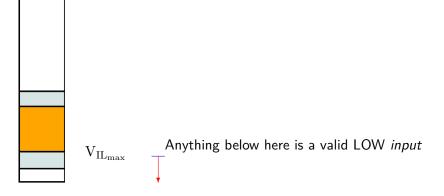

$\bullet~V_{IL_{\rm max}}$

イロト イヨト イヨト

3

Voltage Limits Noise Immunity 3.3V Logic 3.3V outputs into 5V input 5V tolerant inputs 5V INtolerant inputs

## $\bullet \ V_{IH_{min}}$

the *minimum* input voltage which will be accepted as a logic 1.

$\bullet~V_{IL_{\rm max}}$

the maximum input voltage which will be accepted as a logic 0.

イロト イボト イヨト イヨト

Voltage Limits Noise Immunity 3.3V Logic 3.3V outputs into 5V input 5V tolerant inputs 5V INtolerant inputs

## $\bullet \ V_{IH_{\min}}$

the *minimum* input voltage which will be accepted as a logic 1.

$\bullet~V_{IL_{\rm max}}$

the maximum input voltage which will be accepted as a logic 0.

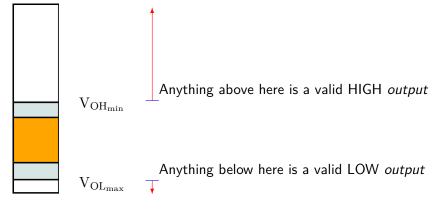

$\bullet \ V_{OH_{\min}}$

イロト イポト イヨト イヨト

Voltage Limits Noise Immunity 3.3V Logic 3.3V outputs into 5V inputs 5V tolerant inputs 5V INtolerant inputs

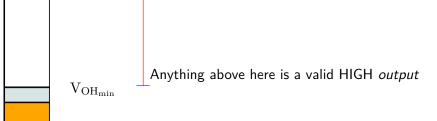

## $\bullet \ V_{IH_{\min}}$

the *minimum* input voltage which will be accepted as a logic 1.

$\bullet~V_{IL_{\rm max}}$

the maximum input voltage which will be accepted as a logic 0.

$\bullet \ V_{OH_{\min}}$

the *minimum* output voltage representing a logic 1 state.

イロト イポト イヨト イヨト

Voltage Limits Noise Immunity 3.3V Logic 3.3V outputs into 5V input 5V tolerant inputs 5V INtolerant inputs

## $\bullet \ V_{IH_{\min}}$

the *minimum* input voltage which will be accepted as a logic 1.

$\bullet~V_{IL_{max}}$

the maximum input voltage which will be accepted as a logic 0.

$\bullet \ V_{OH_{\min}}$

the *minimum* output voltage representing a logic 1 state.

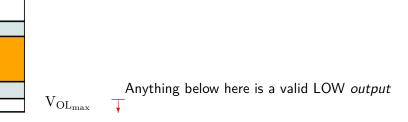

•  $V_{OL_{max}}$

Voltage Limits Noise Immunity 3.3V Logic 3.3V outputs into 5V input 5V tolerant inputs 5V INtolerant inputs

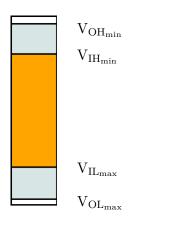

# $\bullet \ V_{IH_{\min}}$

the *minimum* input voltage which will be accepted as a logic 1.

$\bullet \ V_{IL_{max}}$

the maximum input voltage which will be accepted as a logic 0.

$\bullet \ V_{OH_{\min}}$

the minimum output voltage representing a logic 1 state.

$\bullet \ V_{OL_{max}}$

the *maximum* output voltage representing a logic 0 state.

-

Voltage Limits Noise Immunity 3.3V Logic 3.3V outputs into 5V input 5V tolerant inputs 5V INtolerant inputs

For the 3 logic families to be studied, the *specified* values of these parameters are given in the following table.

イロト イボト イヨト イヨト

Voltage Limits Noise Immunity 3.3V Logic 3.3V outputs into 5V input 5V tolerant inputs 5V INtolerant inputs

For the 3 logic families to be studied, the *specified* values of these parameters are given in the following table. In other words, real gates should perform *at least as well* as the values listed.

| Family         | $V_{\rm IH_{min}}$ | $V_{\mathrm{IL}_{\mathrm{max}}}$ | $V_{\rm OH_{min}}$     | $V_{OL_{\max}}$   |

|----------------|--------------------|----------------------------------|------------------------|-------------------|

| TTL            | 2.0                | 0.8                              | 2.4                    | 0.4               |

| LSTTL          | 2.0                | 0.8                              | 2.7                    | 0.5               |

| HC(CMOS)       | $0.75 V_{DD}$      | $0.25 \mathrm{V_{DD}}$           | $\mathrm{V_{DD}}$ -0.1 | $V_{\rm SS}$ +0.1 |

| $V_{DD}$ =4.5V | 3.15               | 1.35                             | 4.4                    | 0.1               |

イロト イボト イヨト イヨト

| Ideal logic gates<br>Real logic gates<br>Logic families | Voltage Limits<br>Noise Immunity<br>3.3V Logic<br>3.3V outputs into 5V inputs<br>5V tolerant inputs<br>5V INtolerant inputs |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

|                                                         |                                                                                                                             |

What the above information means is that, (for instance), if both *inputs* to a 7400 TTL NAND gate are at greater than or equal to 2.4 volts, they will be considered "high", and so the *output* should be "low",

伺 ト イヨト イヨト

| Ideal logic ga<br>Real logic ga<br>Logic fami | 3.3V Logic<br>3.3V outputs into 5V inputs |

|-----------------------------------------------|-------------------------------------------|

|                                               |                                           |

What the above information means is that, (for instance), if both *inputs* to a 7400 TTL NAND gate are at greater than or equal to 2.4 volts, they will be considered "high", and so the *output* should be "low", i.e. at a voltage less than or equal to 0.4 volts.

周 ト イ ヨ ト イ ヨ ト

#### Voltage Limits

Noise Immunity 3.3V Logic 3.3V outputs into 5V inputs 5V tolerant inputs 5V INtolerant inputs

$\begin{array}{c} V_{OH_{min}} \\ V_{IH_{min}} \end{array}$

$\begin{array}{l} V_{IL_{max}} \\ V_{OL_{max}} \end{array}$

TTL

・ロト ・回ト ・ヨト ・ヨト

æ

Ideal logic gatesVoltage LimitsReal logic gates.3V LogicLogic families3.3V LogicSV tolerant inputs5V INtolerant inputs

## TTL

イロト イボト イヨト イヨト

Voltage LimitsIdeal logic gatesReal logic gatesLogic familiesSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolutionSolution<td

### TTL

$\mathrm{V}_{\mathrm{IH}_{\mathrm{min}}}$

TTL

イロト イヨト イヨト

イロト イヨト イヨト

Voltage LimitsIdeal logic gatesReal logic gatesLogic familiesSV tolerant inputsSV Intolerant inputs

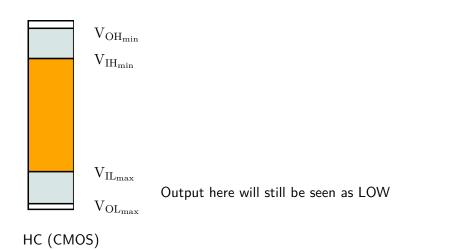

HC (CMOS)

・ロト ・四ト ・ヨト ・ヨト

æ

#### Voltage Limits

Noise Immunity 3.3V Logic 3.3V outputs into 5V inputs 5V tolerant inputs 5V INtolerant inputs

# HC (CMOS) logic

Terry Sturtevant Electronics Logic Family Characteristics: Voltage

・ロト ・回ト ・ヨト ・ヨト

æ

#### Voltage Limits

Noise Immunity 3.3V Logic 3.3V outputs into 5V inputs 5V tolerant inputs 5V INtolerant inputs

# HC (CMOS) logic

Note: For HC (CMOS) logic  $V_{\rm DD}$  can be as low as 2V and as high as 6V.

イロト イボト イヨト イヨト

| ldeal logic gates<br>Real logic gates<br>Logic families | Voltage Limits<br>Noise Immunity<br>3.3V Logic<br>3.3V outputs into 5V inputs<br>5V tolerant inputs<br>5V INtolerant inputs |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

|                                                         |                                                                                                                             |

æ

• For each logic family, you should notice that the *output* voltage limits are more stringent than the *input* voltage limits.

イロト イボト イヨト イヨト

• For each logic family, you should notice that the *output* voltage limits are more stringent than the *input* voltage limits. This is to provide **noise immunity** to the devices.

イロト イボト イヨト イヨト

For each logic family, you should notice that the *output* voltage limits are more stringent than the *input* voltage limits. This is to provide **noise immunity** to the devices.

In other words, if a bit of noise (i.e. voltage fluctuation) were

added to the output of one gate, it should not affect a gate which follows this one.

< ロ > < 同 > < 三 > < 三 >

- For each logic family, you should notice that the *output* voltage limits are more stringent than the *input* voltage limits. This is to provide **noise immunity** to the devices.

In other words, if a bit of noise (i.e. voltage fluctuation) were

- added to the output of one gate, it should not affect a gate which follows this one.

- Imagine what would happen if the limits were the same.

< ロ > < 同 > < 三 > < 三 >

Ideal logic gates<br/>Real logic familiesVoltage Limits<br/>Noise Immunity<br/>3.3V LogicLogic families3.3V Logic<br/>3.3V outputs into 5V inputs<br/>5V tolerant inputs

$\begin{array}{c} V_{OH_{min}} \\ V_{IH_{min}} \end{array}$

$\begin{array}{l} V_{IL_{max}} \\ V_{OL_{max}} \end{array}$

TTL

・ロト ・回ト ・ヨト ・ヨト

æ

イロト イボト イヨト イヨト

$\begin{array}{l} V_{IL_{max}} \\ V_{OL_{max}} \end{array}$

Output here will still be seen as LOW

TTL

イロト イボト イヨト イヨト

Ideal logic gatesVoltage LimitsReal logic gates3.3V LogicLogic families3.3V outputs into 5V inputs5V tolerant inputs5V INtolerant inputs

CMOS

・ロト ・回ト ・ヨト ・ヨト

æ

HC (CMOS)

イロト イヨト イヨト

Voltage Limits Noise Immunity 3.3V Logic SV tolerant inputs SV INtolerant inputs

イロト イボト イヨト イヨト

Ideal logic gates<br/>Real logic familiesVoltage Limits<br/>Noise Immunity<br/>3.3V LogicStructure<br/>Logic familiesNoise Immunity<br/>3.3V LogicStructure<br/>SV tolerant inputsSV Intolerant inputs

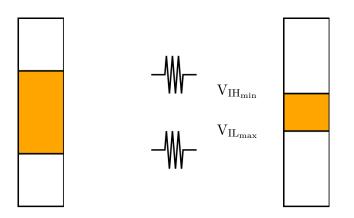

Consider one gate feeding into another.

If a signal gets *noise* added to it, the voltage will fluctuate up and down.

イロト イボト イヨト イヨト

A certain amount of noise will still leave the resulting signal within the *input* limits of the second gate.

イロト イヨト イヨト

Ideal logic gates<br/>Real logic gates<br/>Logic familiesVoltage Limits<br/>Noise Immunity<br/>3.3V Logic<br/>3.3V outputs into 5V inputs<br/>5V tolerant inputs<br/>5V INtolerant inputs

The difference between the output and input limits is the **noise immunity**.

| deal logic gates<br>Real logic gates<br>Logic families | Voltage Limits<br>Noise Immunity<br>3.3V Logic<br>3.3V outputs into 5V inputs<br>5V tolerant inputs<br>5V INtolerant inputs |

|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

|                                                        |                                                                                                                             |

æ

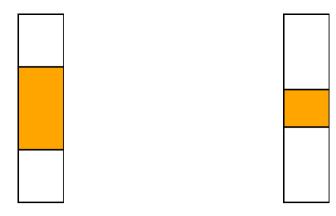

As devices are getting smaller, and aiming for lower power, many are running on voltages lower than 5V. One common voltage for many devices, including internal circuitry on the Raspberry Pi, is 3.3V.

- As devices are getting smaller, and aiming for lower power, many are running on voltages lower than 5V. One common voltage for many devices, including internal circuitry on the Raspberry Pi, is 3.3V.

- The input and output limits are similar to standard TTL.

イロト イポト イヨト ・

- As devices are getting smaller, and aiming for lower power, many are running on voltages lower than 5V. One common voltage for many devices, including internal circuitry on the Raspberry Pi, is 3.3V.

- The input and output limits are similar to standard TTL.

Note: Even though the voltage limits are similar to 5V TTL, voltages above 3.3V may damage the device, so you can't directly connect to 5V logic.

Voltage Limits Noise Immunity **3.3V Logic 3.3V outputs 5V tolerant inputs 5V INtolerant inputs**

3.3V logic

5V logic

#### 3.3V HC

э

イロト イボト イヨト イヨト

Terry Sturtevant Electronics Logic Family Characteristics: Voltage

Voltage Limits Noise Immunity 3.3V Logic **3.3V outputs into 5V inputs** 5V tolerant inputs 5V INtolerant inputs

## 3.3V outputs into 5V inputs

・ロト ・四ト ・ヨト ・ヨト

Voltage Limits Noise Immunity 3.3V Logic **3.3V outputs into 5V inputs** 5V tolerant inputs 5V INtolerant inputs

## 3.3V outputs into 5V inputs

Because of the voltage limits of 3.3V and 5V logic, devices with 3.3V outputs will usually be OK feeding into 5V devices.

(日)

Voltage Limits Noise Immunity 3.3V Logic **3.3V outputs into 5V inputs** 5V tolerant inputs 5V INtolerant inputs

# 3.3V outputs into 5V inputs

Because of the voltage limits of 3.3V and 5V logic, devices with 3.3V outputs will usually be OK feeding into 5V devices.

Note: As long as no signals go into the 3.3V logic from the 5V logic, 3.3V and 5V logic devices can usually be connected directly.

<ロト < 同ト < ヨト < ヨト

Voltage Limits Noise Immunity Real logic gates Logic families SV tolerant inputs SV INtolerant inputs

## 5V tolerant inputs

・ロト ・回ト ・ヨト ・ヨト

3

## 5V tolerant inputs

• Some devices which run on 3.3V supplies will still have inputs which are **5V tolerant**.

イロト イポト イヨト イヨト

# 5V tolerant inputs

- Some devices which run on 3.3V supplies will still have inputs which are **5V tolerant**.

- This means that 5V voltages on the inputs won't damage the device.

イロト イボト イヨト イヨト

# 5V tolerant inputs

- Some devices which run on 3.3V supplies will still have inputs which are **5V tolerant**.

- This means that 5V voltages on the inputs won't damage the device.

Note: Most devices which run on 3.3V supplies are *not* 5V tolerant.

イロト イボト イヨト イヨト

Voltage Limits Noise Immunity 3.3V Logic 3.3V outputs into 5V inputs 5V tolerant inputs 5V INtolerant inputs

# 5V INtolerant inputs

Terry Sturtevant Electronics Logic Family Characteristics: Voltage

3

Voltage Limits Noise Immunity Real logic gates Logic families SV Intolerant inputs

# 5V INtolerant inputs

• For 3.3V devices with inputs which are *not* 5V tolerant, a *voltage divider* can be used.

イロト イボト イヨト イヨト

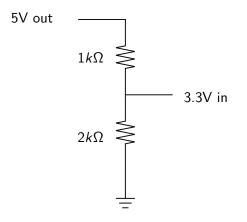

# 5V INtolerant inputs

- For 3.3V devices with inputs which are *not* 5V tolerant, a *voltage divider* can be used.

- Since  $3.3 = \frac{2}{3}(5)$ , a resistor ratio of 1:2 should work.

イロト イボト イヨト イヨト

# 5V INtolerant inputs

- For 3.3V devices with inputs which are *not* 5V tolerant, a *voltage divider* can be used.

- Since  $3.3 = \frac{2}{3}(5)$ , a resistor ratio of 1:2 should work.

Note: Current limts must be observed; typical resistor values are  $1k\Omega$  and  $2k\Omega$ .

イロト イボト イヨト イヨト

| Ideal logic gates<br>Real logic gates<br>Logic families | Voltage Limits<br>Noise Immunity<br>3.3V Logic<br>3.3V outputs into 5V inputs<br>5V tolerant inputs<br><b>5V INtolerant inputs</b> |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

ヘロア ヘロア ヘヨア ヘヨア

æ