# Electronics Logic Gate Characteristics: Current

## Terry Sturtevant

Wilfrid Laurier University

September 4, 2013

Terry Sturtevant Electronics Logic Gate Characteristics: Current

<ロト <回ト < 回ト < 回ト < 回ト -

nar

Э

Operating current limits TTL connections CMOS connections

# Current convention

Terry Sturtevant Electronics Logic Gate Characteristics: Current

ヘロト 人間 ト 人臣 ト 人臣 ト

3

Operating current limits TTL connections CMOS connections

# Current convention

By convention, current into a chip is positive, so current out of a chip is negative.

イロト イボト イヨト イヨト

MQ (P

Operating current limits TTL connections CMOS connections

# Operating current limits

Terry Sturtevant Electronics Logic Gate Characteristics: Current

・ロト ・回ト ・ヨト ・ヨト

Э

Operating current limits TTL connections CMOS connections

# Operating current limits

Gates have current limits as well as voltage limits.

・ロト ・ 一下・ ・ ヨト・

Э

DQ P

Operating current limits TTL connections CMOS connections

# Operating current limits

Gates have current limits as well as voltage limits.

There are limits to the input and output currents of each individual gate.

イロト イボト イヨト イヨト

MQ (P

Operating current limits TTL connections CMOS connections

# Operating current limits

Gates have current limits as well as voltage limits.

There are limits to the input and output currents of each individual gate.

In addition, there is some current required by the chip itself, as long as power is applied.

・ロト ・ 一下・ ・ ヨト・

MQ (P

Operating current limits TTL connections CMOS connections

# Output current limits; example

Terry Sturtevant Electronics Logic Gate Characteristics: Current

イロト イボト イヨト イヨト

900

Э

Operating current limits TTL connections CMOS connections

# Output current limits; example

Terry Sturtevant Electronics Logic Gate Characteristics: Current

< ロ > < 回 > < 回 > < 回 > < 回 >

DQC

Operating current limits TTL connections CMOS connections

# Output current limits; example

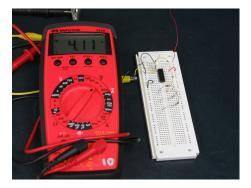

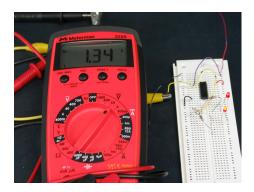

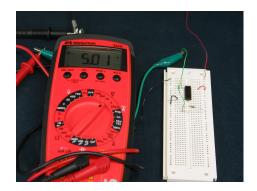

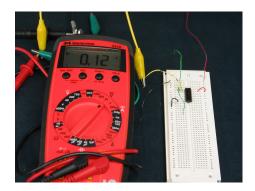

Here's a TTL gate (LS04) producing a HIGH output with no load.

イロト イボト イヨト イヨト

MQ (P

Operating current limits TTL connections CMOS connections

#### The output voltage with no load is 4.11 Volts.

<ロト <回ト < 三ト < 三ト

Э

Operating current limits TTL connections CMOS connections

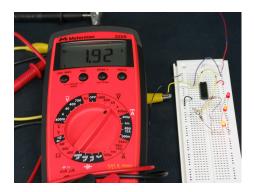

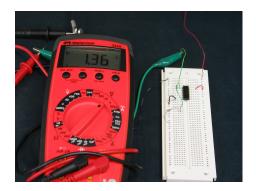

With an LED with a  $5.1k\Omega$  resistor, the output voltage has dropped.

Terry Sturtevant Electronics Logic Gate Characteristics: Current

イロト イボト イヨト イヨト

Operating current limits TTL connections CMOS connections

Note that the current being drawn is less than 1 mA.

・ロト ・四ト ・ヨト ・ヨト

Э

Operating current limits TTL connections CMOS connections

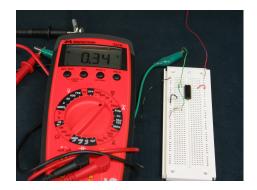

With an LED with a  $1k\Omega$  resistor, the output voltage has dropped further.

イロト イボト イヨト イヨト

Operating current limits TTL connections CMOS connections

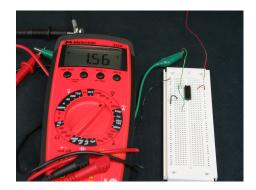

With an LED with a  $100\Omega$  resistor, the output voltage has dropped further.

Terry Sturtevant Electronics Logic Gate Characteristics: Current

イロト イボト イヨト イヨト

Operating current limits TTL connections CMOS connections

With two LEDs with  $100\Omega$  resistors, the output voltage has dropped further.

Terry Sturtevant Electronics Logic Gate Characteristics: Current

イロト イボト イヨト イヨト

Operating current limits TTL connections CMOS connections

With three LEDs with  $100\Omega$  resistors, the output voltage has dropped further.

◆□ ▶ ◆□ ▶ ◆ □ ▶ ◆ □ ▶

nar

э

Operating current limits TTL connections CMOS connections

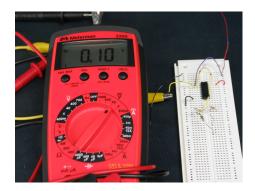

Here's the same TTL gate (LS04) producing a LOW output with no load.

イロト イボト イヨト イヨト

Operating current limits TTL connections CMOS connections

The output voltage with no load is 0.10 Volts.

< ロ > < 回 > < 回 > < 回 > < 回 >

Operating current limits TTL connections CMOS connections

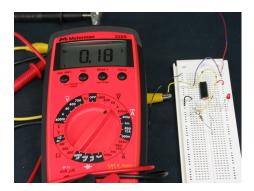

With an LED with a  $5.1k\Omega$  *pull-up* resistor, the output voltage has risen.

イロト イボト イヨト イヨト

Operating current limits TTL connections CMOS connections

The output voltage with less than 1mA load is 0.17 Volts.

◆□ ▶ ◆□ ▶ ◆ □ ▶ ◆ □ ▶

Operating current limits TTL connections CMOS connections

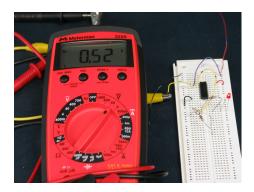

With an LED with a  $1k\Omega$  resistor, the output voltage has risen further.

< ロ > < 回 > < 回 > < 回 > < 回 >

SQR

Operating current limits TTL connections CMOS connections

With an LED with a  $100\Omega$  resistor, the output voltage has risen further.

< ロ > < 回 > < 回 > < 回 > < 回 >

Operating current limits TTL connections CMOS connections

With two LEDs with  $100\Omega$  resistors, the output voltage has risen further.

イロト イボト イヨト イヨト

Operating current limits TTL connections CMOS connections

With three LEDs with  $100\Omega$  resistors, the output voltage has risen further.

Terry Sturtevant Electronics Logic Gate Characteristics: Current

イロト イボト イヨト イヨト

Operating current limits TTL connections CMOS connections

# Input current requirements

Terry Sturtevant Electronics Logic Gate Characteristics: Current

イロト イボト イヨト イヨト

900

э

Operating current limits TTL connections CMOS connections

## Input current requirements

# When the inputs of a gate are unconnected, they are neither HIGH nor LOW.

イロト イボト イヨト イヨト

MQ (P

Operating current limits TTL connections CMOS connections

## Input current requirements

When the inputs of a gate are unconnected, they are neither HIGH nor LOW.

They are said to be **floating**.

イロト イボト イヨト イヨト

MQ (P

Operating current limits TTL connections CMOS connections

# Input current limits; example

Terry Sturtevant Electronics Logic Gate Characteristics: Current

イロト イボト イヨト イヨト

900

э

Operating current limits TTL connections CMOS connections

# Input current limits; example

Terry Sturtevant Electronics Logic Gate Characteristics: Current

< ロ > < 回 > < 回 > < 回 > < 回 >

Operating current limits TTL connections CMOS connections

# Input current limits; example

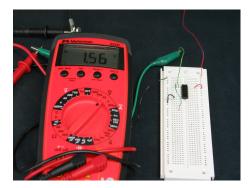

Here's the voltage on the input of a TTL gate (LS04) when left floating.

イロト イボト イヨト イヨト

MQ (P

Operating current limits TTL connections CMOS connections

Notice that the input voltage is not valid for either HIGH or LOW.

◆□ ▶ ◆□ ▶ ◆ □ ▶ ◆ □ ▶

Operating current limits TTL connections CMOS connections

With a  $10k\Omega$  resistor to  $V_{cc}$ , the input is now a valid HIGH.

・ロト ・四ト ・ヨト ・ヨト

900

э

Operating current limits TTL connections CMOS connections

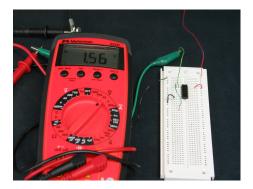

With a  $10k\Omega$  resistor to GROUND, though, the input is **not** a valid LOW.

Terry Sturtevant Electronics Logic Gate Characteristics: Current

◆□ ▶ ◆□ ▶ ◆ □ ▶ ◆ □ ▶

Operating current limits TTL connections CMOS connections

### With a $5.1k\Omega$ resistor to GROUND the input is a valid LOW.

◆□ ▶ ◆□ ▶ ◆ □ ▶ ◆ □ ▶

Operating current limits TTL connections CMOS connections

What's the output when the inputs are floating?

◆□ ▶ ◆□ ▶ ◆ □ ▶ ◆ □ ▶

Operating current limits TTL connections CMOS connections

The output (in this case) is a valid LOW, *as though* the input were a valid HIGH.

イロト イボト イヨト イヨト

nar

Operating current limits TTL connections CMOS connections

#### Output current limits; Connecting gates

Terry Sturtevant Electronics Logic Gate Characteristics: Current

イロト イボト イヨト イヨト

э

Operating current limits TTL connections CMOS connections

#### Output current limits; Connecting gates

When the output of one gate is used as the input of another gate, the *output* section of the first gate must source (or sink) enough current so that the *input* voltage of the second gate is within the proper range.

イロト イポト イヨト イヨト

Operating current limits TTL connections CMOS connections

#### Output current limits; Connecting gates

When the output of one gate is used as the input of another gate, the *output* section of the first gate must source (or sink) enough current so that the *input* voltage of the second gate is within the proper range.

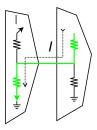

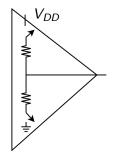

The output of different types of gates is more similar than the inputs functionally, and an equivalent circuit is given in the following figure.

<ロト < 同ト < ヨト < ヨト :

Operating current limits TTL connections CMOS connections

#### TTL input current limits

Terry Sturtevant Electronics Logic Gate Characteristics: Current

・ロト ・回ト ・ヨト ・ヨト

Э

Operating current limits TTL connections CMOS connections

#### TTL input current limits

◆□ ▶ ◆□ ▶ ◆ □ ▶ ◆ □ ▶

Э

Operating current limits TTL connections CMOS connections

#### TTL input current limits

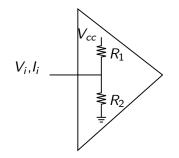

This is an equivalent circuit for a TTL gate input.

イロト イボト イヨト イヨト

Operating current limits TTL connections CMOS connections

#### TTL connections

Terry Sturtevant Electronics Logic Gate Characteristics: Current

・ロト ・ 日 ト ・ 日 ト ・ 日 ト ・

E

Operating current limits TTL connections CMOS connections

#### TTL connections

◆□▶ ◆□▶ ◆臣▶ ◆臣▶

E

Operating current limits TTL connections CMOS connections

#### TTL connections

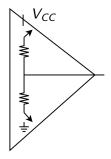

This is an equivalent circuit for a gate *output*.

・ロト ・四ト ・ヨト ・ヨト

э

イロト イヨト イヨト

Э

イロト イボト イヨト イヨト

Э

Current flows out of gate

イロト イボト イヨト イヨト

MQ (P

Current flows *out of* gate Voltage must stay above  $V_{IH_{min}}$

イロト イボト イヨト イヨト

MQ (P

イロト イヨト イヨト

Э

Operating current limits TTL connections CMOS connections

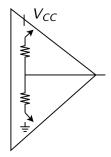

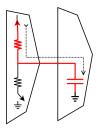

Here's what happens when a TTL LOW output feeds into another TTL input.

イロト イボト イヨト イヨト

Current flows into gate

イロト イボト イヨト イヨト

MQ (P

Current flows into gate Voltage must stay below  $V_{lL_{max}}$

イロト イボト イヨト イヨト

MQ (P

#### The input to a logic gate is not like an ideal voltmeter.

イロト イヨト イヨト

3

The input to a logic gate is not like an ideal voltmeter. Consider the equivalent circuit shown in the following figure.

・ロト ・ 戸 ト ・ ヨ ト ・ ヨ ト ・

Э

Operating current limits TTL connections CMOS connections

#### TTL input analysis

Terry Sturtevant Electronics Logic Gate Characteristics: Current

・ロト ・回ト ・ヨト ・ヨト

E

Operating current limits TTL connections CMOS connections

#### TTL input analysis

Terry Sturtevant Electronics Logic Gate Characteristics: Current

・ロト ・日ト ・日ト ・日ト

E

Operating current limits TTL connections CMOS connections

#### TTL input analysis

$$V_{cc} \\ R_1 \\ \downarrow \\ R_2 \\ \downarrow \\ R_2$$

This is an equivalent circuit for a TTL gate input.

イロト イボト イヨト イヨト

Э

イロト イヨト イヨト

Э

$$V_i = \left(\frac{V_{cc} - V_i}{R_1} + I_i\right) R_2$$

イロト イヨト イヨト

Э

$$V_i = \left(\frac{V_{cc} - V_i}{R_1} + I_i\right) R_2$$

and thus

$$V_{i} = \left(V_{cc}\frac{R_{2}}{R_{1}} + I_{i}R_{2}\right)\frac{R_{1}}{R_{1} + R_{2}}$$

イロト イヨト イヨト

Э

$$V_i = \left(\frac{V_{cc} - V_i}{R_1} + I_i\right) R_2$$

and thus

$$V_{i} = \left(V_{cc}\frac{R_{2}}{R_{1}} + I_{i}R_{2}\right)\frac{R_{1}}{R_{1} + R_{2}}$$

(Note that in order to make  $V_i$  low,  $I_i$  will have to be negative.)

・ロト ・ 同 ト ・ ヨ ト ・ ヨ ト

MQ (P

Logic gate operating currents

Total power consumption Interfacing families; CMOS to TTL and TTL to CMOS Operating current limits TTL connections CMOS connections

#### TTL

Terry Sturtevant Electronics Logic Gate Characteristics: Current

・ロト ・回ト ・ヨト ・ヨト

÷.

Operating current limits TTL connections CMOS connections

#### TTL

### For TTL, the amount of current drawn by producing a high output is not the same as the amount drawn by a low output.

イロト イボト イヨト イヨト

TL

Operating current limits TTL connections CMOS connections

## For TTL, the amount of current drawn by producing a high output is not the same as the amount drawn by a low output. Thus there are two quantities,

イロト イボト イヨト イヨト

TL

Operating current limits TTL connections CMOS connections

# For TTL, the amount of current drawn by producing a high output is not the same as the amount drawn by a low output. Thus there are two quantities, $I_{CCH}$

イロト イボト イヨト イヨト

TL

Operating current limits TTL connections CMOS connections

# For TTL, the amount of current drawn by producing a high output is not the same as the amount drawn by a low output. Thus there are two quantities, $I_{CCH}$ and $I_{CCL}$ .

イロト イヨト イヨト

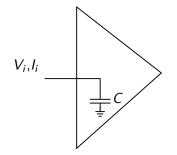

Since CMOS is based on FETs rather than BJTs, the input current required is very small, but the input capacitance of the gate must be considered.

イロト イボト イヨト イヨト

Since CMOS is based on FETs rather than BJTs, the input current required is very small, but the input capacitance of the gate must be considered.

The following figure shows the equivalent circuit for a CMOS input.

イロト イボト イヨト イヨト

MQ (P

Operating current limits TTL connections CMOS connections

#### CMOS input current limits

Terry Sturtevant Electronics Logic Gate Characteristics: Current

・ロト ・回ト ・ヨト ・ヨト

900

Operating current limits TTL connections CMOS connections

#### CMOS input current limits

◆□ ▶ ◆□ ▶ ◆ □ ▶ ◆ □ ▶

900

Э

Operating current limits TTL connections CMOS connections

# CMOS input current limits

This is an equivalent circuit for a CMOS gate input.

イロト イボト イヨト イヨト

Operating current limits TTL connections CMOS connections

# **CMOS** connections

Terry Sturtevant Electronics Logic Gate Characteristics: Current

◆□▶ ◆□▶ ◆三▶ ◆三▶

3

990

Operating current limits TTL connections CMOS connections

# **CMOS** connections

◆□▶ ◆□▶ ◆臣▶ ◆臣▶

E

990

Operating current limits TTL connections CMOS connections

# **CMOS** connections

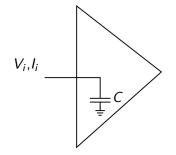

The equivalent circuit for a CMOS *output* is similar to TTL.

イロト イボト イヨト イヨト

# Here's what happens when a CMOS HIGH output feeds into another CMOS input.

・ロト ・ 戸 ト ・ ヨ ト ・ ヨ ト ・

Э

SQR

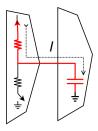

Here's what happens when a CMOS HIGH output feeds into another CMOS input.

イロト イボト イヨト イヨト

Э

SQR

Operating current limits TTL connections CMOS connections

Here's what happens when a CMOS HIGH output feeds into another CMOS input.

Current flows out of gate

イロト イボト イヨト イヨト

Operating current limits TTL connections CMOS connections

Here's what happens when a CMOS HIGH output feeds into another CMOS input.

Current flows *out of* gate Voltage must rise above  $V_{IH_{min}}$

イロト イボト イヨト イヨト

# Here's what happens when a CMOS LOW output feeds into another CMOS input.

・ロト ・ 戸 ト ・ ヨ ト ・ ヨ ト ・

Э

SQR

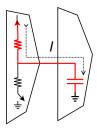

Here's what happens when a CMOS LOW output feeds into another CMOS input.

イロト イボト イヨト イヨト

Operating current limits TTL connections CMOS connections

Here's what happens when a CMOS LOW output feeds into another CMOS input.

Current flows into gate

イロト イボト イヨト イヨト

Operating current limits TTL connections CMOS connections

Here's what happens when a CMOS LOW output feeds into another CMOS input.

Current flows into gate Voltage must fall below  $V_{lL_{max}}$

イロト イボト イヨト イヨト

For CMOS, even though the output equivalent circuit is similar to that of a TTL gate, when one gate is connected to another there is a limit to the *speed* at which the second gate will change due to the time it takes for the input capacitor to charge or discharge.

イロト イヨト イヨト

For CMOS, even though the output equivalent circuit is similar to that of a TTL gate, when one gate is connected to another there is a limit to the *speed* at which the second gate will change due to the time it takes for the input capacitor to charge or discharge.

Since the gate input is capacitive, then the current drawn from the previous gate will start big and get smaller as the capacitor reaches its intended voltage.

イロト イポト イヨト イヨト

Operating current limits TTL connections CMOS connections

# CMOS

Terry Sturtevant Electronics Logic Gate Characteristics: Current

・ロト ・回ト ・ヨト ・ヨト

E

990

Operating current limits TTL connections CMOS connections

# **CMOS**

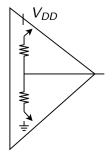

For CMOS, the symmetry of the internals means that the current needed to produce a high output is the same as the amount drawn by a low output.

・ロト ・ 戸 ト ・ ヨ ト ・ ヨ ト ・

Operating current limits TTL connections CMOS connections

# **CMOS**

For CMOS, the symmetry of the internals means that the current needed to produce a high output is the same as the amount drawn by a low output.

Thus there is only one quantity,

・ロト ・ 戸 ト ・ ヨ ト ・ ヨ ト ・

Operating current limits TTL connections CMOS connections

# **CMOS**

For CMOS, the symmetry of the internals means that the current needed to produce a high output is the same as the amount drawn by a low output.

Thus there is only one quantity,  $I_{DD_{max}}$

イロト イヨト イヨト

Quiescent current

### Total power consumption

Terry Sturtevant Electronics Logic Gate Characteristics: Current

・ロト ・回ト ・ヨト ・ヨト

Э

900

Quiescent current

### Total power consumption

The power consumption of the device is given by

イロト イボト イヨト イヨト

Quiescent current

### Total power consumption

The power consumption of the device is given by

$$P = V_{supply} \times I_{total}$$

Terry Sturtevant Electronics Logic Gate Characteristics: Current

イロト イボト イヨト イヨト

Quiescent current

#### Total power consumption

The power consumption of the device is given by

$$P = V_{supply} imes I_{total}$$

where  $I_{total}$  is the sum of the currents drawn by each of the gates on the device.

イロト イポト イヨト イヨト

The power drawn by a circuit is the sum of the power drawn by each device in the circuit.

イロト イポト イヨト イヨト

Э

SQR

The power drawn by a circuit is the sum of the power drawn by each device in the circuit.

The supply must be able to provide as much as needed by the whole circuit.

イロト イポト イヨト イヨト

Quiescent current

#### Quiescent current

Terry Sturtevant Electronics Logic Gate Characteristics: Current

E

990

Quiescent current

#### Quiescent current

As long as power is applied to a chip, it will be drawing a small amount of current.

イロト イヨト イヨト

Э

< ロ > < 回 > < 回 > < 回 > < 回 > <</p>

3

590

An output limit, for instance, can be seen as either how much is guaranteed to be *supplied*, or as how much can be safely *demanded*.

イロト イヨト イヨト

1

An output limit, for instance, can be seen as either how much is guaranteed to be *supplied*, or as how much can be safely *demanded*.

In other words, the limit can be seen as either belonging to the *device* or the the *surrounding* circuit.

イロト イヨト イヨト

An output limit, for instance, can be seen as either how much is guaranteed to be *supplied*, or as how much can be safely *demanded*.

In other words, the limit can be seen as either belonging to the *device* or the the *surrounding* circuit.

While they are functionally equivalent, the first view will give a *minimum* for a quantity while the second will give a *maximum*.

イロト イヨト イヨト

An output limit, for instance, can be seen as either how much is guaranteed to be *supplied*, or as how much can be safely *demanded*.

In other words, the limit can be seen as either belonging to the *device* or the the *surrounding* circuit.

While they are functionally equivalent, the first view will give a *minimum* for a quantity while the second will give a *maximum*.

Different manufacturers may take either view, and so it is important to understand this so that you can make sense of whichever you are given.

イロト イヨト イヨト

#### Four particular quantities are of interest in specifying the tolerance:

イロト イヨト イヨト

Э

SQR

<ロト < 部 ト < 注 ト < 注 ト - 注 。</p>

990

#### $\textcircled{1} I_{IL_{max}}$

the *maximum* input current which must be drawn from a gate's input to ground to guarantee the input will be low.

イロト イヨト イヨト

1

### $\textcircled{1} I_{IL_{max}}$

the *maximum* input current which must be drawn from a gate's input to ground to guarantee the input will be low.

${\rm 2 \hspace{-0.5mm} I}_{IH_{max}}$

イロト イポト イヨト イヨト

Э

### $\textcircled{1} I_{IL_{max}}$

the *maximum* input current which must be drawn from a gate's input to ground to guarantee the input will be low.

${\rm 2 \hspace{0.4mm} I}_{IH_{max}}$

the *maximum* input current which must be supplied to a gate's input to guarantee the input will be high.

イロト イヨト イヨト

the *maximum* input current which must be drawn from a gate's input to ground to guarantee the input will be low.

${\rm 2 \hspace{0.4mm}} I_{IH_{max}}$

the *maximum* input current which must be supplied to a gate's input to guarantee the input will be high.

${\rm ③}~I_{OH_{max}}$

イロト イヨト イヨト

1

the *maximum* input current which must be drawn from a gate's input to ground to guarantee the input will be low.

${\rm 2 \hspace{0.4mm}} I_{IH_{max}}$

the *maximum* input current which must be supplied to a gate's input to guarantee the input will be high.

${\rm ③}~I_{OH_{max}}$

the *maximum* current which the gate can source through its output and still keep the output high.

イロト イポト イヨト イヨト

the *maximum* input current which must be drawn from a gate's input to ground to guarantee the input will be low.

${\rm 2 \hspace{0.4mm}} I_{IH_{max}}$

the *maximum* input current which must be supplied to a gate's input to guarantee the input will be high.

${\rm ③}~I_{OH_{max}}$

the *maximum* current which the gate can source through its output and still keep the output high.

I<sub>OLmax</sub>

イロト イポト イヨト イヨト

the *maximum* input current which must be drawn from a gate's input to ground to guarantee the input will be low.

${\rm 2 \hspace{0.4mm}} I_{IH_{max}}$

the *maximum* input current which must be supplied to a gate's input to guarantee the input will be high.

${\rm ③}~I_{OH_{max}}$

the *maximum* current which the gate can source through its output and still keep the output high.

I<sub>OLmax</sub>

the *maximum* current which the gate can sink through its output and still keep the output low.

イロト イヨト イヨト

#### $I_{IL_{\rm max}}$ and $I_{IH_{\rm max}}$ may require some explanation.

◆□ ▶ ◆□ ▶ ◆三 ▶ ◆三 ▶ ● ○ ● ● ●

イロト イヨト イヨト

-

Logic gate operating currents Total power consumption Interfacing families; CMOS to TTL and TTL to CMOS

$I_{IL_{max}}$  and  $I_{IH_{max}}$  may require some explanation. Most people assume that if the inputs of a gate are not attached to anything they will be treated as logic low. This is a bad assumption.

イロト 人間ト イヨト イヨト

-

This is a bad assumption.

An important piece of information about various logic families is what happens when inputs are left to **float**; i.e. remain unconnected.

イロト イヨト イヨト

This is a bad assumption.

An important piece of information about various logic families is what happens when inputs are left to **float**; i.e. remain unconnected.

They may float high, low or anywhere in between.

イロト イヨト イヨト

This is a bad assumption.

An important piece of information about various logic families is what happens when inputs are left to **float**; i.e. remain unconnected.

They may float high, low or anywhere in between.

To have an input recognized as something other than its "floating" state will require that a finite amount of current be either supplied to the input (to make it high) or drawn from the input to ground (to make it low.)

イロト 人間ト イヨト イヨト

This is a bad assumption.

An important piece of information about various logic families is what happens when inputs are left to **float**; i.e. remain unconnected.

They may float high, low or anywhere in between.

To have an input recognized as something other than its "floating" state will require that a finite amount of current be either supplied to the input (to make it high) or drawn from the input to ground (to make it low.)

Never assume anything about unconnected inputs.

イロト 人間ト イヨト イヨト

This is a bad assumption.

An important piece of information about various logic families is what happens when inputs are left to **float**; i.e. remain unconnected.

They may float high, low or anywhere in between.

To have an input recognized as something other than its "floating" state will require that a finite amount of current be either supplied to the input (to make it high) or drawn from the input to ground (to make it low.)

Never assume anything about unconnected inputs.

If you want them to be in a particular state, tie them that way.

・ロト ・ 同ト ・ ヨト ・ ヨト

# These current limits are referred to as the *fan-in* and *fan-out* characteristics of digital circuits.

イロト イポト イヨト イヨト

3

SQR

These current limits are referred to as the *fan-in* and *fan-out* characteristics of digital circuits.

Note that a given gate will occasionally have zero for either  $I_{IL_{\rm max}}$  or  $I_{IH_{\rm max}}.$

イロト イポト イヨト イヨト

1

Logic gate operating currents Total power consumption Interfacing families; CMOS to TTL and TTL to CMOS

# Interfacing families; CMOS to TTL and TTL to CMOS

Terry Sturtevant Electronics Logic Gate Characteristics: Current

イロト イポト イヨト イヨト

Э

Logic gate operating currents Total power consumption Interfacing families; CMOS to TTL and TTL to CMOS

# Interfacing families; CMOS to TTL and TTL to CMOS

Because different families have different current and voltage requirements, they can't simply be mixed as though they were all the same.

イロト イヨト イヨト

# Interfacing families; CMOS to TTL and TTL to CMOS

Because different families have different current and voltage requirements, they can't simply be mixed as though they were all the same.

Each gate must stay within its required operating parameters.

<ロト < 同ト < ヨト < ヨト -