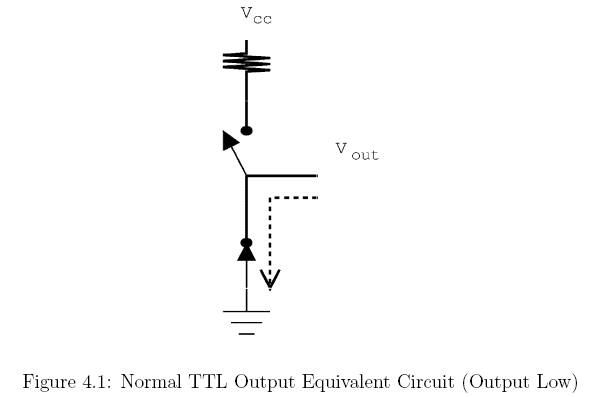

The current limits of normal logic gates are reduced with open collector gates (if using TTL) or open drain gates (with CMOS). The two types of gates are functionally equivalent, so it's only necessary to discuss one. The transistors at the outputs of a normal TTL gate can be thought of as switches, so that the circuitry looks as in Figure 4.1. The two switches are always in opposite states, so when the upper switch is open, the lower switch is closed and thus the output is low. (Actually, when the inputs are in the "undefined" region, the transistors are both in a state in between "open" and "closed", and so could be thought of as resistors of some finite value. However we will only discuss the "normal" cases.)

You will note in this case that the device will be sinking current, as indicated by the arrow into the device.

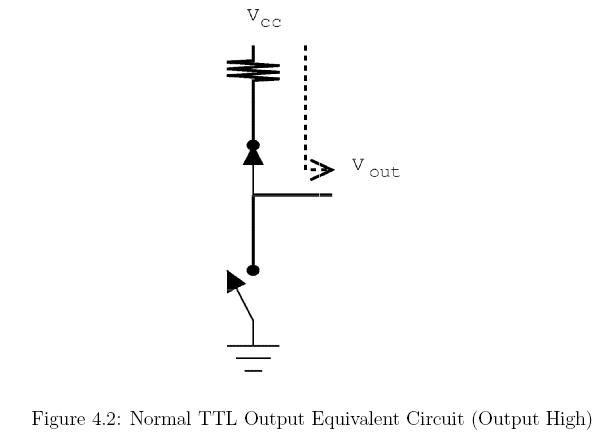

If, on the other hand, the upper switch is closed, and the lower switch is open, so that the circuitry looks as in Figure 4.2, then the output is high (because it is connected to Vcc through the pull-up resistor.) In this case, the gate is sourcing current, as indicated by the arrow coming out of the device.

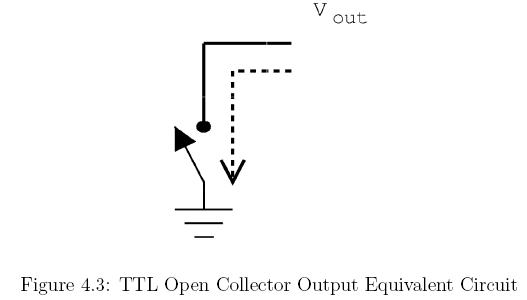

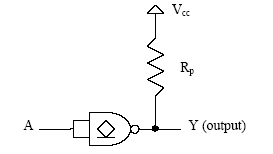

An open collector gate is much simpler; it consists of

only one switch and no resistor, as in Figure 4.3.

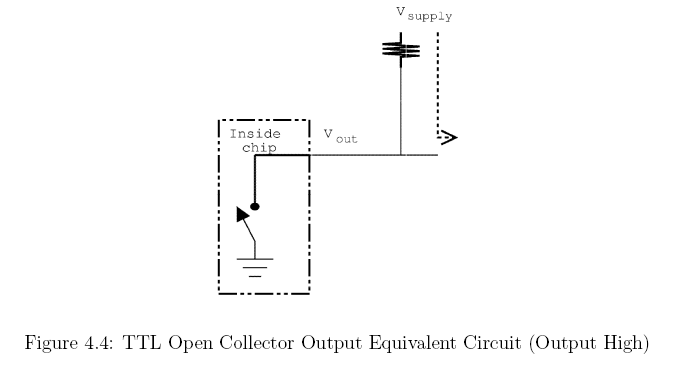

In essence, it only provides low outputs, and relies on an

external pull up resistor to supply high outputs, as shown in

Figure 4.4. The gate will not function properly without the

external pull up resistor. Thus the gate is only ever used to

sink current, and so can be optimized for that function.

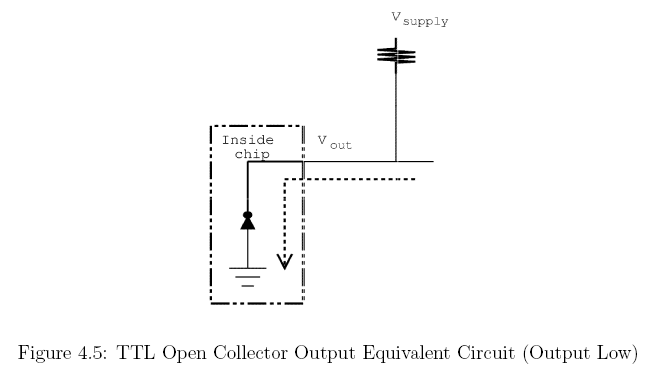

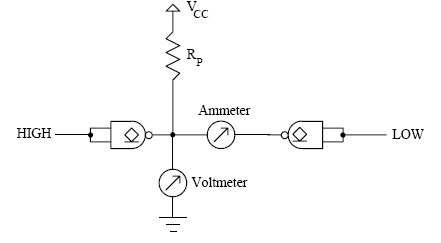

The big advantage to the open collector gate is that it can be used

to provide much higher currents, since it only needs to sink them,

not source them, as in Figure 4.5.

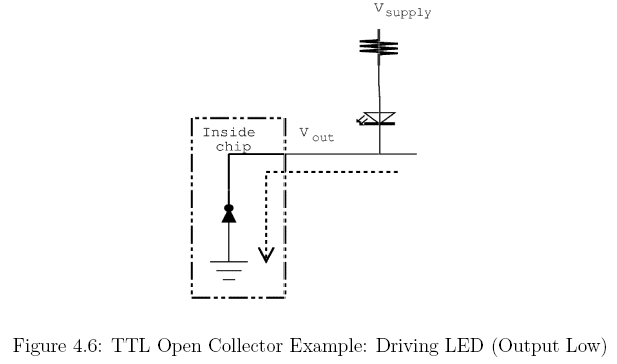

An example of this in use is to drive an output device like an LED

which may require more current than normally provided by a TTL

gate, as in Figure 4.6.

Another possibility with open collector outputs is to drive devices which require a higher voltage than Vcc. Since the gate only needs to sink current, then the voltage connected to the output resistor can be anything, so long as it does not overload the sinking ability of the gate when the output is low. Thus, an open collector gate gives flexibility in output voltage and current for the cost of a bit of extra wiring.

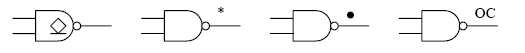

Open collector gates (and open drain gates) typically use one of the following symbols.

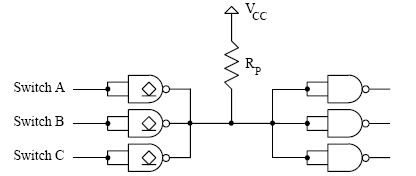

You will have to calculate pull-up resistor values for a

number of the following circuits. See Pull-up resistor calculation for

instructions on calculating the minimum and the maximum resistor

values.

When looking up VOHmin, you'll

need to look at the datasheet for the 74LS00, not the 74LS01.

It's the value for the

family

that matters.

(In fact, the 74LS01 probably doesn't give a value for

VOHmin. Why is that?)

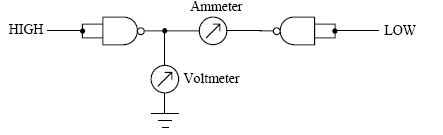

One of the possible uses for open collector gates is to allow wire ANDing of the outputs. This can reduce the number of components in certain circuits. With normal gates, you would need to use AND gates to combine the outputs. You will examine both situations.

|

Caution!

The

following step uses a wired-AND configuration with a

totem-pole output TTL gate. NEVER do this in a real circuit! |

Wilfrid Laurier University

© 2019 Wilfrid Laurier University