# CP316 Serial Communication-UART

Terry Sturtevant

Wilfrid Laurier University

November 8, 2017

Universal Asynchronous Receiver Transmitter

- Universal Asynchronous Receiver Transmitter

- Simplest form of serial communication

- Universal Asynchronous Receiver Transmitter

- Simplest form of serial communication

- Between 2 devices

- Universal Asynchronous Receiver Transmitter

- Simplest form of serial communication

- Between 2 devices

- Uses 2 signals (and Ground), Rx and Tx

- Universal Asynchronous Receiver Transmitter

- Simplest form of serial communication

- Between 2 devices

- Uses 2 signals (and Ground), Rx and Tx

- Asynchronous, so both must agree on baud rate

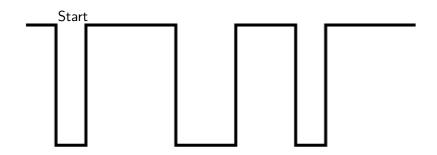

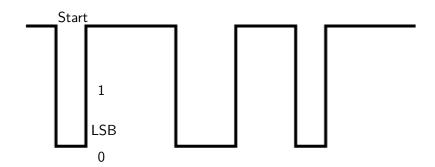

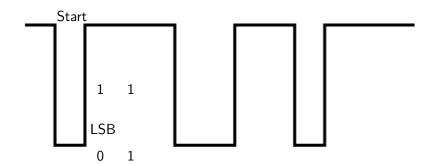

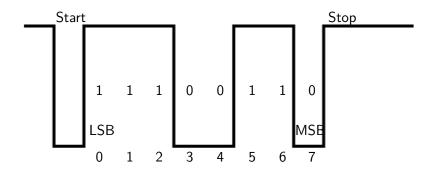

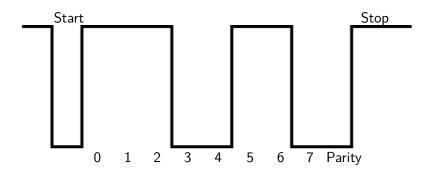

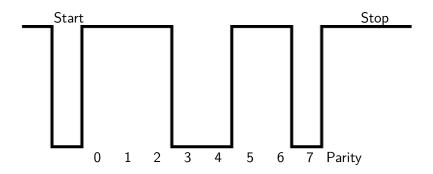

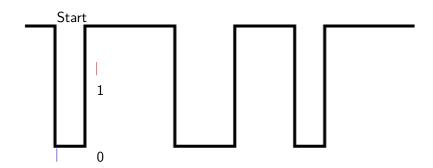

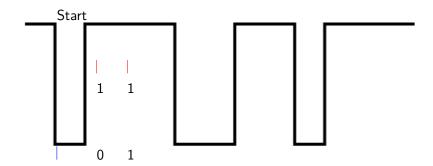

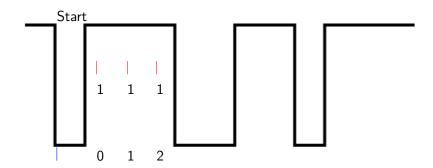

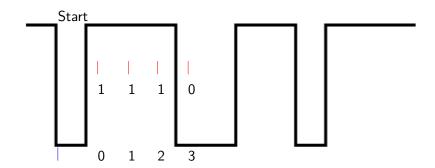

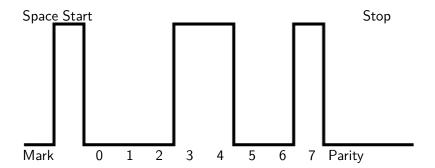

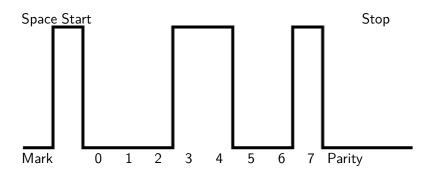

• 1 Start bit at "0" level

- 1 Start bit at "0" level

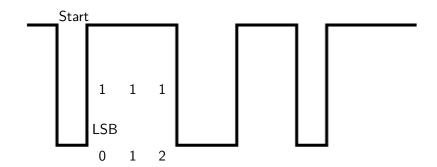

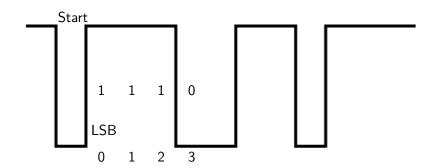

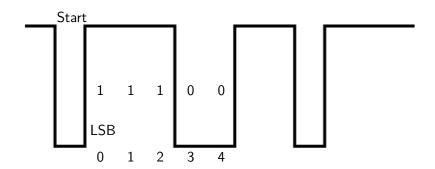

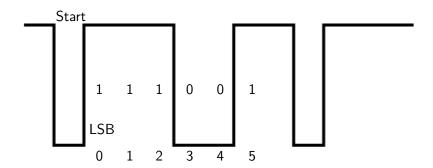

- LSB transmitted first

- 1 Start bit at "0" level

- LSB transmitted first

- Can have odd, even, or no parity bit

- 1 Start bit at "0" level

- LSB transmitted first

- Can have odd, even, or no parity bit

- 1 or 2 Stop bits at "1" level

- 1 Start bit at "0" level

- LSB transmitted first

- Can have odd, even, or no parity bit

- 1 or 2 Stop bits at "1" level

Since start and stop bits are opposite, new characters can always be detected.

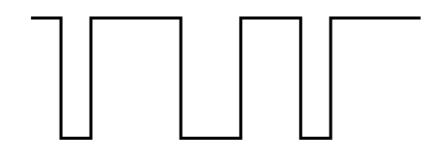

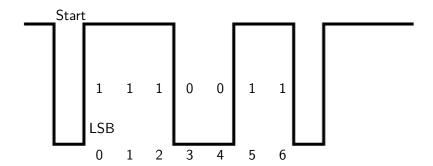

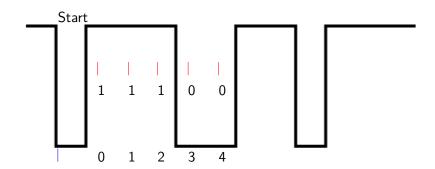

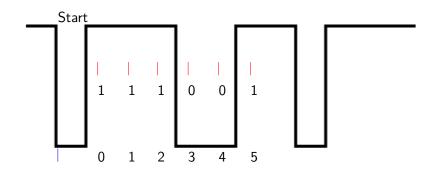

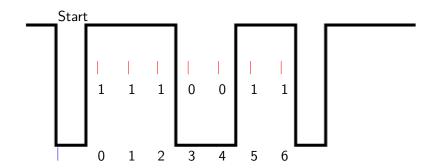

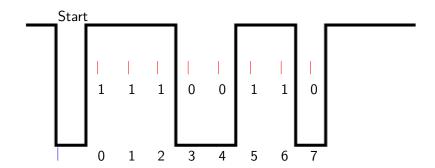

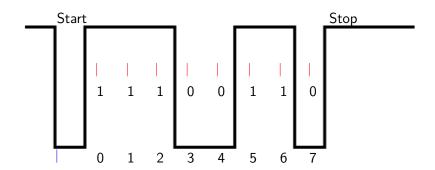

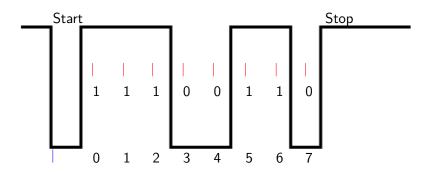

**UART** no parity - 01100111

**UART** even parity

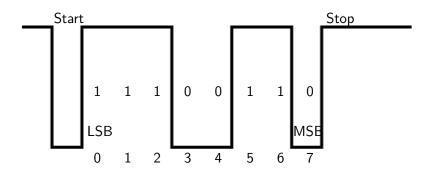

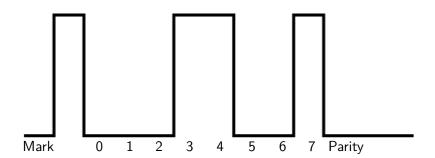

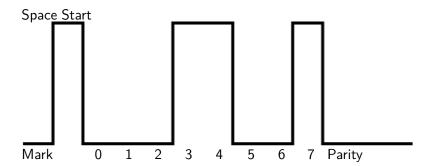

**UART** odd parity

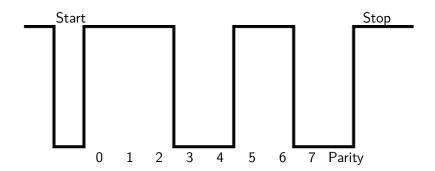

• Baud rate is the number of bits possible in a second

- Baud rate is the number of bits possible in a second

- ullet e.g. 9600 baud ightarrow 1 bit takes  $rac{1}{9600}$  second

- Baud rate is the number of bits possible in a second

- ullet e.g. 9600 baud ightarrow 1 bit takes  $rac{1}{9600}$  second

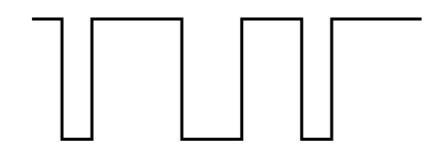

- After start bit is detected, wait time for  $1\frac{1}{2}$  bit to test for first data bit and then after every 1 bit interval

- Baud rate is the number of bits possible in a second

- ullet e.g. 9600 baud ightarrow 1 bit takes  $rac{1}{9600}$  second

- After start bit is detected, wait time for  $1\frac{1}{2}$  bit to test for first data bit and then after every 1 bit interval

- Resetting at the start bit allows some clock variation

Bit timing

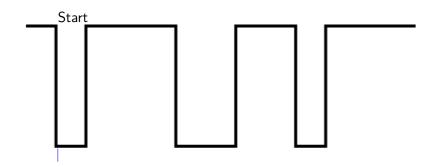

Voltages are inverted

- Voltages are inverted

- $\pm 3 \rightarrow \pm 12$

- Voltages are inverted

- $\bullet$   $\pm 3 \rightarrow \pm 12$

- Zero is not a valid voltage

- Voltages are inverted

- $\pm 3 \rightarrow \pm 12$

- Zero is not a valid voltage

- ullet Mark level (inactive/1) is a negative voltage

- Voltages are inverted

- $\bullet$   $\pm 3 \rightarrow \pm 12$

- Zero is not a valid voltage

- Mark level (inactive/1) is a negative voltage

- Space level (active/0) is a positive voltage

RS232 levels

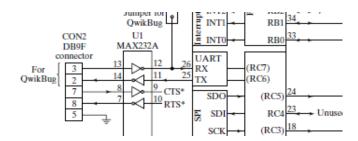

QwikFlash modules

QwikFlash modules ramifications???

QwikFlash modules ramifications??? interrupts; transmit and receive

QwikFlash modules ramifications??? interrupts; transmit and receive

$\rightarrow$  Sections 6.4.5 to 6.4.7

QwikFlash modules ramifications??? interrupts; transmit and receive

- $\rightarrow$  Sections 6.4.5 to 6.4.7

- $\rightarrow$  Section 8.2

2 wires, one-to-one

2 wires, one-to-one EIA232 (RS232)

2 wires, one-to-one EIA232 (RS232)

→ Section 9.3

2 wires, one-to-one EIA232 (RS232)

$\rightarrow$  Section 9.3

**USART** registers

2 wires, one-to-one

EIA232 (RS232)

$\rightarrow$  Section 9.3

**USART** registers

$\rightarrow$  Section 9.4.1

2 wires, one-to-one

EIA232 (RS232)

$\rightarrow$  Section 9.3

**USART** registers

$\rightarrow$  Section 9.4.1

USART asynchronous mode

2 wires, one-to-one

EIA232 (RS232)

$\rightarrow$  Section 9.3

**USART** registers

$\rightarrow$  Section 9.4.1

USART asynchronous mode

$\rightarrow$  Section 9.4.2

2 wires, one-to-one

EIA232 (RS232)

$\rightarrow$  Section 9.3

**USART** registers

$\rightarrow$  Section 9.4.1

USART asynchronous mode

$\rightarrow$  Section 9.4.2

USART asynchronous mode to EIA232

2 wires, one-to-one

EIA232 (RS232)

$\rightarrow$  Section 9.3

**USART** registers

$\rightarrow$  Section 9.4.1

USART asynchronous mode

$\rightarrow$  Section 9.4.2

USART asynchronous mode to EIA232

$\rightarrow$  Section 9.4.5

2 wires, one-to-one

EIA232 (RS232)

$\rightarrow$  Section 9.3

**USART** registers

$\rightarrow$  Section 9.4.1

USART asynchronous mode

$\rightarrow$  Section 9.4.2

USART asynchronous mode to EIA232

- $\rightarrow$  Section 9.4.5

- $\rightarrow$  Section 16.0

2 wires (+ ground), one-to-one

2 wires (+ ground), one-to-one TX

```

2 wires (+ ground), one-to-one

```

TX

RX

2 wires (+ ground), one-to-one

TX

RX

Fixed baud rate, common to both devices

```

2 wires (+ ground), one-to-one

```

TX

RX

Fixed baud rate, common to both devices

At least one start bit

```

2 wires (+ ground), one-to-one

```

TX

RX

Fixed baud rate, common to both devices

At least one start bit

At least one stop bit

```

2 wires (+ ground), one-to-one

```

ΤX

RX

Fixed baud rate, common to both devices

At least one start bit

At least one stop bit

voltage levels not TTL; inverted (normally)

```

2 wires (+ ground), one-to-one TX RX Fixed baud rate, common to both devices At least one start bit At least one stop bit voltage levels not TTL; inverted (normally) (except "TTL serial" devices)

```

```

2 wires (+ ground), one-to-one

TX

RX

Fixed baud rate, common to both devices

At least one start bit

At least one stop bit

voltage levels not TTL; inverted (normally)

(except "TTL serial" devices)

packets are single characters

```

## **Qwikflash UART connections**

## Qwikflash UART connections

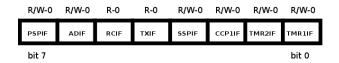

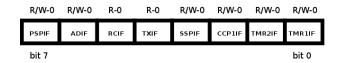

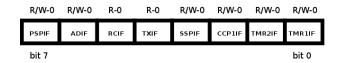

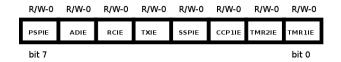

Bits in PIR1 register

Bits in PIR1 register - Note RCIF, TXIF

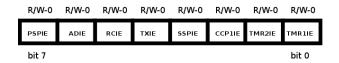

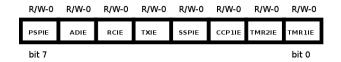

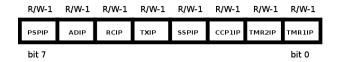

Bits in PIE1 register

Bits in PIE1 register - Note RCIE, TXIE

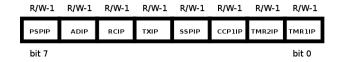

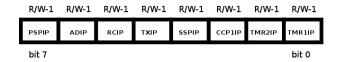

Bits in IPR1 register

Bits in IPR1 register - Note RCIP, TXIP

overview

overview reasons

overview reasons *NIB*

PORT configuration

#### PORT configuration

$\rightarrow$  macro or subroutine?

### PORT configuration

$\rightarrow$  macro or subroutine?

Initiallization

#### PORT configuration

$\rightarrow \mathsf{macro} \ \mathsf{or} \ \mathsf{subroutine?}$

Initiallization

$\rightarrow$  macro or subroutine?

#### PORT configuration

$\rightarrow \mathsf{macro} \ \mathsf{or} \ \mathsf{subroutine?}$

Initiallization

$\rightarrow$  macro or subroutine?

Write to device

#### PORT configuration

$\rightarrow \ \mathsf{macro} \ \mathsf{or} \ \mathsf{subroutine?}$

Initiallization

$\rightarrow$  macro or subroutine?

Write to device

$\rightarrow$  macro or subroutine?

#### PORT configuration

$\rightarrow$  macro or subroutine?

Initiallization

$\rightarrow$  macro or subroutine?

Write to device

$\rightarrow$  macro or subroutine?

Read from device

#### PORT configuration

$\rightarrow$  macro or subroutine?

Initiallization

$\rightarrow$  macro or subroutine?

Write to device

$\rightarrow$  macro or subroutine?

Read from device

$\rightarrow$  macro or subroutine?