# CP316 Introduction

Terry Sturtevant

Wilfrid Laurier University

November 8, 2017

### Introduction to the PIC Microcontroller

$\mu {\sf PU}$  vs.  $\mu {\sf CU}$  vs. DSP

$\mu PU$  vs.  $\mu CU$  vs. DSP

$\rightarrow$  Section 1.2.2

$\mu {\sf PU}$  vs.  $\mu {\sf CU}$  vs. DSP

- $\rightarrow$  Section 1.2.2

- $\rightarrow$  Section 1.4

```

\mu {\sf PU} vs. \mu {\sf CU} vs. DSP

```

- $\rightarrow$  Section 1.2.2

- $\rightarrow$  Section 1.4

QwikFlash Board

$\mu {\sf PU}$  vs.  $\mu {\sf CU}$  vs. DSP

- $\rightarrow$  Section 1.2.2

- $\rightarrow$  Section 1.4

QwikFlash Board

MPLABX IDE

Oscillator options

Memory organization ile Registers and Access Bank pecial Registers

## Oscillator configurations

Oscillator options

Memory organization

File Registers and Access Bar

# Oscillator configurations

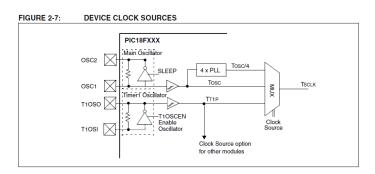

$\rightarrow$  Section 2.0

Oscillator options

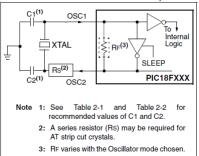

FIGURE 2-1: CRYSTAL/CERAMIC

RESONATOR OPERATION

(HS, XT OR LP

CONFIGURATION)

#### Oscillator options Memory organizat

lemory organization ile Registers and Access Bank pecial Registers

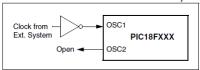

FIGURE 2-2: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

### Oscillator options Memory organizati

Memory organization ile Registers and Access Bank pecial Registers

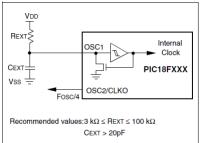

### Figure 2-3

FIGURE 2-3: RC OSCILLATOR MODE

The RCIO Oscillator mode functions like the RC mode, except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6).

Oscillator options Memory organization

FIGURE 2-4: EXTERNAL CLOCK INPUT OPERATION (EC CONFIGURATION)

### Oscillator options

lemory organization ile Registers and Access Bank pecial Registers

FIGURE 2-5: EXTERNAL CLOCK INPUT OPERATION (ECIO CONFIGURATION)

Oscillator options

lemory organization le Registers and Access Banl pecial Registers

# Oscillator options Memory organization File Registers and Ac

Oscillator options

Memory organization

File Registers and Access B

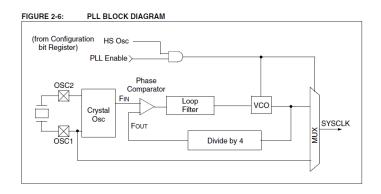

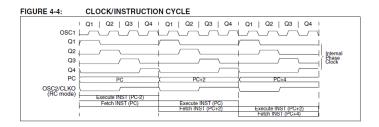

### Figure 4-4

# Oscillator options Memory organization File Registers and Access Bank

### Figure 4-4

Oscillator options

Memory organization ile Registers and Access Bank pecial Registers

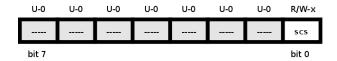

### OSCCON register

### OSCCON register

Oscillator configuration register

### OSCCON register

Oscillator configuration register

$\rightarrow$  Section 2.6.1

## OSCCON register

### Oscillator configuration register

$\rightarrow$  Section 2.6.1

### OSCCON register

Oscillator configuration register

$\rightarrow$  Section 2.6.1

Bits in OSCCON register

## Memory organization

# Memory organization

# Memory organization

### Modified Harvard Architechture

$\rightarrow$  Section 1.5.1

# Memory organization

- $\rightarrow$  Section 1.5.1

- $\rightarrow$  Section 14.3

# Memory organization

- $\rightarrow$  Section 1.5.1

- $\rightarrow$  Section 14.3

- $\rightarrow$  Section 1.11.1

# Memory organization

- $\rightarrow$  Section 1.5.1

- $\rightarrow$  Section 14.3

- $\rightarrow$  Section 1.11.1

- $\rightarrow$  Section 4.0

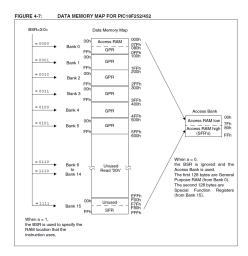

## Data memory

### Data memory

$\mathsf{Data} \ \mathsf{memory} \ \mathsf{location} \ \to \mathsf{File} \ \mathsf{Register}$

Data memory location  $\rightarrow$  File Register

**GPRs**

**SFRs**

Data memory location  $\rightarrow$  File Register

**GPRs**

**SFRs**

$\rightarrow$  Section 4.9

Data memory location  $\rightarrow$  File Register

**GPRs**

**SFRs**

$\rightarrow$  Section 4.9

Access bank

Data memory location  $\rightarrow$  File Register

**GPRs**

**SFRs**

$\rightarrow$  Section 4.9

Access bank

$\rightarrow$  Section 4.10

Data memory location  $\rightarrow$  File Register

**GPRs**

**SFRs**

$\rightarrow$  Section 4.9

Access bank

$\rightarrow$  Section 4.10

**BSR**

Data memory location  $\rightarrow$  File Register

**GPRs**

**SFRs**

$\rightarrow$  Section 4.9

Access bank

$\rightarrow$  Section 4.10

**BSR**

$\rightarrow$  Section 4.11

Data memory location  $\rightarrow$  File Register

**GPRs**

**SFRs**

$\rightarrow$  Section 4.9

Access bank

$\rightarrow$  Section 4.10

**BSR**

$\rightarrow$  Section 4.11

No software stack!

Data memory location  $\rightarrow$  File Register

**GPRs**

**SFRs**

$\rightarrow$  Section 4.9

Access bank

$\rightarrow$  Section 4.10

**BSR**

$\rightarrow$  Section 4.11

#### No software stack!

$\rightarrow$  Section 1.5.4

Data memory location  $\rightarrow$  File Register

**GPRs**

**SFRs**

$\rightarrow$  Section 4.9

Access bank

$\rightarrow$  Section 4.10

**BSR**

$\rightarrow$  Section 4.11

#### No software stack!

- $\rightarrow$  Section 1.5.4

- $\rightarrow$  Section 4.2

# File Registers and Access Bank

# File Registers and Access Bank

### Features

### Features

RISC architecture

### **Features**

RISC architecture

$\rightarrow$  Section 1.11.1

### **Features**

RISC architecture

- $\rightarrow$  Section 1.11.1

- $\rightarrow$  Section 1.4

### **Features**

#### RISC architecture

- $\rightarrow$  Section 1.11.1

- $\rightarrow$  Section 1.4

- $\rightarrow$  Section 20.0

### **Features**

RISC architecture

- $\rightarrow$  Section 1.11.1

- $\rightarrow$  Section 1.4

- $\rightarrow$  Section 20.0

Simple assembler

### **Features**

RISC architecture

- $\rightarrow$  Section 1.11.1

- $\rightarrow$  Section 1.4

- $\rightarrow$  Section 20.0

Simple assembler

$\rightarrow$  Section 1.9

### **Features**

#### RISC architecture

- $\rightarrow$  Section 1.11.1

- $\rightarrow$  Section 1.4

- $\rightarrow$  Section 20.0

Simple assembler

- $\rightarrow$  Section 1.9

- $\rightarrow$  Section 21.2

# W Register

# W Register

Working register

# W Register

Working register

$\rightarrow$  Section 1.6

# W Register

Working register

$\rightarrow$  Section 1.6

also SFR 0xFE8

# W Register

Working register

$\rightarrow$  Section 1.6

also SFR 0xFE8

$\rightarrow$  Section 1.0

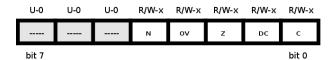

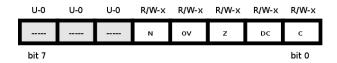

# STATUS register

# STATUS register

Status register

# STATUS register

Status register

$\rightarrow \text{Section } 1.6$

# STATUS register

#### Status register

- $\rightarrow$  Section 1.6

- $\rightarrow$  Section 4.13

# STATUS register

#### Status register

- $\rightarrow$  Section 1.6

- $\rightarrow$  Section 4.13

# STATUS register

#### Status register

- $\rightarrow$  Section 1.6

- $\rightarrow$  Section 4.13

Bits in STATUS register

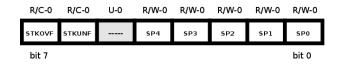

# STKPTR register

# STKPTR register

| R/C-0  | R/C-0  | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|--------|-----|-------|-------|-------|-------|-------|

| STKOVF | STKUNF |     | SP4   | SP3   | SP2   | SP1   | SP0   |

| bit 7  |        |     |       |       |       |       | bit 0 |

# STKPTR register

Bits in STKPTR register