### CP316 Serial Communication-I2C

Terry Sturtevant

Wilfrid Laurier University

November 8, 2017

## Serial Communication - 12C

Inter-Integrated Circuit Interface

- Inter-Integrated Circuit Interface

- Master/slave communication

- Inter-Integrated Circuit Interface

- Master/slave communication

- Uses 2 signals (and Ground),

SDA and SCL

- Inter-Integrated Circuit Interface

- Master/slave communication

- Uses 2 signals (and Ground),

SDA and SCL

- Many slaves can be on the same bus since each has an address

- Inter-Integrated Circuit Interface

- Master/slave communication

- Uses 2 signals (and Ground),

SDA and SCL

- Many slaves can be on the same bus since each has an address

Device addresses are pre-programmed, but can usually be

changed

- Inter-Integrated Circuit Interface

- Master/slave communication

- Uses 2 signals (and Ground),

SDA and SCL

- Many slaves can be on the same bus since each has an address

Device addresses are pre-programmed, but can usually be

changed

- Synchronous, so master controls clock rate

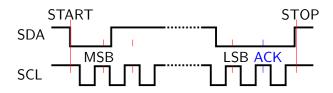

- $1^2$ C; bits are read when SCL is HIGH

- ACK is sent by receiver if OK sender must release SDA after LSB

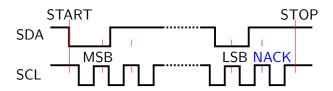

- $1^2$ C; bits are read when SCL is HIGH

- NACK is sent by master-receiver if OK sender must release SDA after LSB

Serial Communication -I2C Serial Communication Bit-bashing Code

Serial Communication -I2C Serial Communication Bit-bashing Code

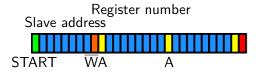

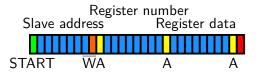

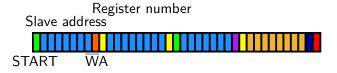

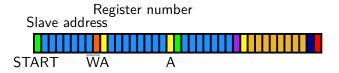

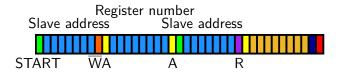

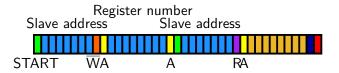

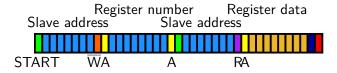

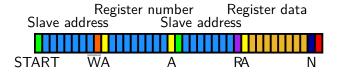

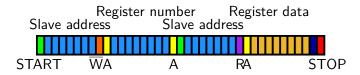

$\bullet$   $I^2C$  read from slave register

$\bullet$   $I^2C$  read from slave register

QwikFlash modules

QwikFlash modules ramifications???

QwikFlash modules ramifications??? interrupts; transmit and receive

QwikFlash modules ramifications??? interrupts; transmit and receive

$\rightarrow$  Sections 6.4.5 to 6.4.7

QwikFlash modules ramifications??? interrupts; transmit and receive

- $\rightarrow$  Sections 6.4.5 to 6.4.7

- $\rightarrow$  Section 8.2

### Master Synchronous Serial Port (MSSP) module

### Master Synchronous Serial Port (MSSP) module

2 modes; **SPI** and  $I^2C$

### Master Synchronous Serial Port (MSSP) module

2 modes; SPI and  $I^2C$

$\rightarrow$  Section 15.0 -15.2

2 wires, master-multiple slave

2 wires, master-multiple slave overview

2 wires, master-multiple slave overview

$\rightarrow$  Section 11.2

2 wires, master-multiple slave overview

$\rightarrow$  Section 11.2

I<sup>2</sup>C module

2 wires, master-multiple slave overview

$\rightarrow$  Section 11.2

I<sup>2</sup>C module

$\rightarrow$  Sections 11.3 to 11.6

2 wires, master-multiple slave overview

$\rightarrow$  Section 11.2

I<sup>2</sup>C module

- $\rightarrow$  Sections 11.3 to 11.6

- $\rightarrow$  Section 15.4

2 wires (+ ground), one-to-many

```

2 wires (+ ground), one-to-many SCL (from master)

```

```

2 wires (+ ground), one-to-many

SCL (from master)

SDA (serial data)

```

```

2 wires (+ ground), one-to-many

SCL (from master)

SDA (serial data)

data transmission rate set by SCL

```

```

2 wires (+ ground), one-to-many

SCL (from master)

SDA (serial data)

data transmission rate set by SCL

address for each device, preset (but possibly programmable)

```

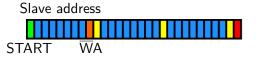

```

2 wires (+ ground), one-to-many

SCL (from master)

SDA (serial data)

data transmission rate set by SCL

address for each device, preset (but possibly programmable)

packets are complex; address of recipient, read or write, data

(variable number of bytes)

```

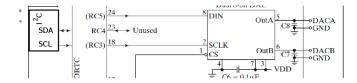

# Qwikflash I<sup>2</sup>C connections

# Qwikflash I<sup>2</sup>C connections

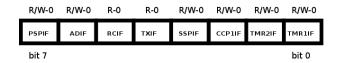

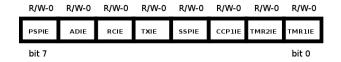

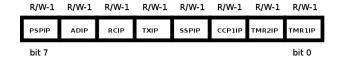

Bits in PIR1 register

Bits in PIR1 register - Note SSPIF

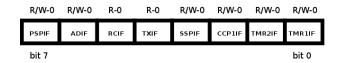

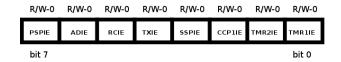

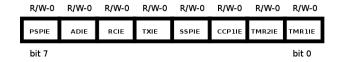

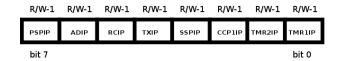

Bits in PIE1 register

Bits in PIE1 register - Note SSPIE

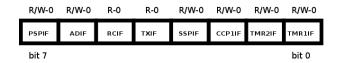

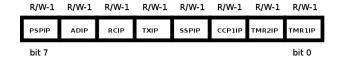

Bits in IPR1 register

Bits in IPR1 register - Note SSPIP

overview

overview reasons

overview reasons *NIB*

PORT configuration

#### PORT configuration

$\rightarrow$  macro or subroutine?

PORT configuration

$\rightarrow$  macro or subroutine?

Initiallization

#### PORT configuration

$\rightarrow \mathsf{macro} \; \mathsf{or} \; \mathsf{subroutine?}$

Initiallization

$\rightarrow$  macro or subroutine?

#### PORT configuration

$\rightarrow \mathsf{macro} \ \mathsf{or} \ \mathsf{subroutine?}$

Initiallization

$\rightarrow$  macro or subroutine?

Write to device

#### PORT configuration

$\rightarrow \mathsf{macro} \ \mathsf{or} \ \mathsf{subroutine?}$

Initiallization

$\rightarrow$  macro or subroutine?

Write to device

$\rightarrow$  macro or subroutine?

#### PORT configuration

$\rightarrow$  macro or subroutine?

Initiallization

$\rightarrow$  macro or subroutine?

Write to device

$\rightarrow$  macro or subroutine?

Read from device

#### PORT configuration

$\rightarrow$  macro or subroutine?

Initiallization

$\rightarrow$  macro or subroutine?

Write to device

$\rightarrow$  macro or subroutine?

Read from device

$\rightarrow$  macro or subroutine?