## PIC18F452 Timer adjustment

Terry Sturtevant

Wilfrid Laurier University

February 10, 2012

Here's a code fragment for the timer:

Here's a code fragment for the timer:

```

timeadj equ d'65536'-d'25000'+d'12'+2

```

```

read 16 bit counter

movff TMR0L, templ

movff TMR0H, temph

; get buffered high half

movlw low time_adj

; add time adjustment

addwf templ, F

movlw high timeadi

addwfc temph, F

movff

temph, TMR0H

; pre-load high half

movff templ, TMR0L

: write 16 bit counter

bcf

INTCON.TMR0IF

; clear flag

```

Whether using polling or interrupts, this section of code is used to reload the timer after an overflow.

Whether using polling or interrupts, this section of code is used to reload the timer after an overflow.

Following is an explanation of what it does, and why it's important.

Whether using polling or interrupts, this section of code is used to reload the timer after an overflow.

Following is an explanation of what it does, and why it's important.

For instance, the line timeadj equ d'65536'-d'25000'+d'12'+2 needs some explanation.

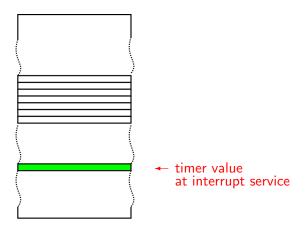

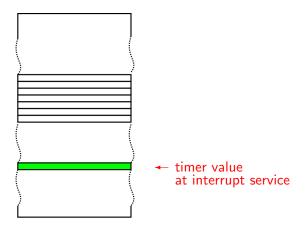

From the interrupt, (or after the flag is polled), until it gets processed, some time passes.

Probably only a few cycles, but important for precise timing.

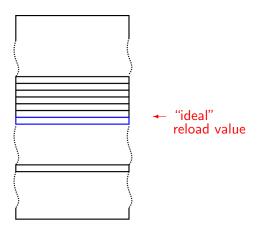

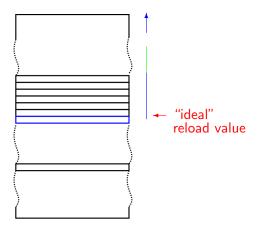

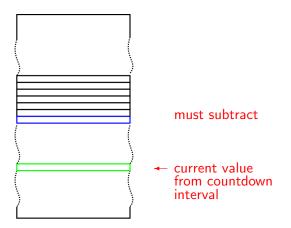

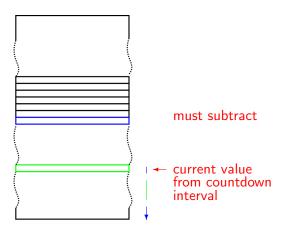

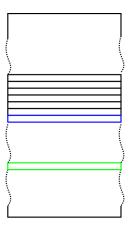

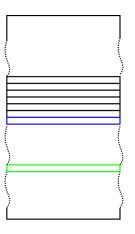

Interval desired is from "ideal" value to overflow (eg. FFFF)

For instance, for an interval of 25000 cycles, we would nominally want to reload with d'65536'-d'25000'

We must subtract the time that happened before the interrupt service (or poll response).

movff TMR0L,templ

First we must load the timer value, low byte first. This latches the high byte.

$movff\ TMR0H, temph$

As we read the (latched) high timer byte, time is passing (2 cycles for this instruction).

movlw low adjust

movlw low adjust

As we begin the subtraction, time is still passing (2 cycles for this instruction; 4 so far).

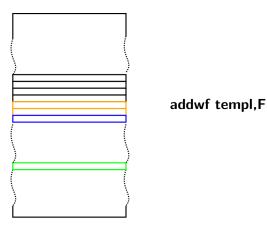

addwf templ,F

(Actually, instead of subtracting, we add to the reload value.)

Time is still passing (2 cycles for this instruction; 6 so far).

movlw high adjust

movlw high adjust

Time is still passing (2 cycles for this instruction; 8 so far).

$addwfc\ temph, F$

$addwfc\ temph, F$

Time is still passing (2 cycles for this instruction; 10 so far).

$mov ff\ temph, TMR0H$

movff temph, TMR0H

Time is still passing (2 cycles for this instruction; 12 so far).

When we rewrite the low byte, the timer will be updated....

.. but there is a 2 cycle delay for the clock to resynch after re-loading.

resynch delay

In total, there are 14 cycles used by the update, which must be subtracted from the desired interval.

resynch delay

As above, these 14 cycles used by the update actually need to be added to the reload value.

resynch delay

After the adjustment is complete, the timer flag must be cleared.

d'65536'

the number of counts in a 16 bit sequence, including zero

- d'65536'

- the number of counts in a 16 bit sequence, including zero

- interval length (in clock cycles)

- d'65536'

the number of counts in a 16 bit sequence, including zero

interval length (in clock cycles)

- interval length (in clock cycles) (eg. d'25000')

- d'65536'

the number of counts in a 16 bit sequence, including zero

- interval length (in clock cycles) (eg. d'25000')

- + d'12'

- d'65536'

the number of counts in a 16 bit sequence, including zero

- interval length (in clock cycles) (eg. d'25000')

- + d'12'

to allow for the time for the arithmetic

- d'65536'

the number of counts in a 16 bit sequence, including zero

- interval length (in clock cycles) (eg. d'25000')

- + d'12'

to allow for the time for the arithmetic

- + 2

to allow for the time for clock resynch

- d'65536'

the number of counts in a 16 bit sequence, including zero

- interval length (in clock cycles) (eg. d'25000')

- + d'12'

to allow for the time for the arithmetic

- + 2

to allow for the time for clock resynch

and then the flag must be cleared for the next interval.