# CP316 Pulse Width Modulation

Terry Sturtevant

Wilfrid Laurier University

January 24, 2020

• timers vs. counters

timers vs. counters

A timer counts clock pulses; a counter counts external events

timers vs. counters

A timer counts clock pulses; a counter counts external events size (i.e. number of bits)

timers vs. counters

A timer counts clock pulses; a counter counts external events size (i.e. number of bits) output pins

• timers vs. counters

A timer counts clock pulses; a counter counts external events size (i.e. number of bits) output pins prescaler

timers vs. counters

```

A timer counts clock pulses; a counter counts external events size (i.e. number of bits) output pins prescaler start/stop

```

timers vs. counters

```

A timer counts clock pulses; a counter counts external events size (i.e. number of bits) output pins prescaler start/stop interrupt flag

```

BOTTOM

#### BOTTOM

value from which the timer starts

- BOTTOM

value from which the timer starts

- MAX

- BOTTOM

- value from which the timer starts

- MAX

maximum value the timer can reach

- BOTTOM value from which the timer starts

- MAX

maximum value the timer can reach

- TOP

- BOTTOM

- value from which the timer starts

- MAX

- maximum value the timer can reach

- TOP

- highest value in the timer count sequence

- BOTTOM

- value from which the timer starts

- MAX

- maximum value the timer can reach

- TOP

highest value in the timer count sequence depending on *mode*, can be less than or equal to MAX

Tn

Tn

Timer n input

- Tn

- Timer n input

- OCnx

- Tn

- Timer *n* input

- OCnx

Output compare pin x for timer n

- Tn

- Timer *n* input

- OCnx

- Output compare pin x for timer n

- ICPn (Timer 1 only)

- **Tn**Timer *n* input

- OCnx

Output compare pin x for timer n

- ICPn (Timer 1 only)

Input capture pin for timer n

TOVn

TOVn

Timer overflow n

- TOVn

- Timer overflow n

- OCFnx

TOVn

Timer overflow *n*

OCFnx

Output compare match x for timer n

TOVn

Timer overflow n

OCFnx

Output compare match x for timer n

• ICFn (Timer 1 only)

TOVn

Timer overflow n

OCFnx

Output compare match x for timer n

ICFn (Timer 1 only)

Input capture for timer n

Fast PWM

• Fast PWM

rolls over at TOP

#### Fast PWM

rolls over at TOP

output OCnx set when compare matches TCNTx and OCRnx

#### Fast PWM

rolls over at TOP output OCnx set when compare matches TCNTx and OCRnx output OCnx cleared at BOTTOM

#### PWM Timer modes

- Fast PWM

- rolls over at TOP

- output OCnx set when compare matches TCNTx and OCRnx output OCnx cleared at BOTTOM

- or vice versa, depending on mode

Phase correct PWM

Phase correct PWM counts BOTTOM to TOP then TOP to BOTTOM

Phase correct PWM

counts BOTTOM to TOP then TOP to BOTTOM output OCnx cleared on upcount, set on downcount when compare matches TCNTx and OCRnx

Phase and frequency correct PWM (Timer 1 only)

Phase and frequency correct PWM (Timer 1 only)

counts BOTTOM to TOP then TOP to BOTTOM

Phase and frequency correct PWM (Timer 1 only)

counts BOTTOM to TOP then TOP to BOTTOM

output set when compare matches TCNT1 and OCR1A or

ICR1

Phase and frequency correct PWM (Timer 1 only)

counts BOTTOM to TOP then TOP to BOTTOM

output set when compare matches TCNT1 and OCR1A or

ICR1

BOTTOM

BOTTOM

$0 \times 00$

BOTTOM

0×00

MAX

BOTTOM

$0 \times 00$

MAX

0xFF

BOTTOM

0x00

MAX

0xFF

maximum value the timer can reach

BOTTOM

0x00

MAX

0xFF

maximum value the timer can reach

TOP

BOTTOM

0x00

MAX

0xFF

maximum value the timer can reach

TOP

MAX or value in OCR0A, depending on mode

# Timer0 prescaler

# Timer0 prescaler

Table 15-9. Clock Select Bit Description

| CS02 | CS01 | CS00 | Description                                             |

|------|------|------|---------------------------------------------------------|

| 0    | 0    | 0    | No clock source (Timer/Counter stopped)                 |

| 0    | 0    | - 1  | clk <sub>NO</sub> /(No prescaling)                      |

| 0    | 1    | 0    | clk <sub>NO</sub> /8 (From prescaler)                   |

| 0    | - 1  | 1    | clk <sub>NO</sub> /64 (From prescaler)                  |

| 1    | 0    | 0    | clk <sub>NO</sub> /256 (From prescaler)                 |

| 1    | 0    | 1    | clk <sub>NO</sub> /1024 (From prescaler)                |

| 1    | - 1  | 0    | External clock source on T0 pin. Clock on falling edge. |

| 1    | - 1  | - 1  | External clock source on T0 pin. Clock on rising edge.  |

If external pin modes are used for the Timer/Counter0, transitions on the T0 pin will clock the counter even if the pin is configured as an output. This feature allows software control of the counting.

# Timer0 prescaler

Table 15-9. Clock Select Bit Description

| CS02 | CS01 | CS00 | Description                                             |

|------|------|------|---------------------------------------------------------|

| 0    | 0    | 0    | No clock source (Timer/Counter stopped)                 |

| 0    | 0    | 1    | clk <sub>NO</sub> /(No prescaling)                      |

| 0    | 1    | 0    | clk <sub>NO</sub> /8 (From prescaler)                   |

| 0    | - 1  | 1    | clk <sub>NO</sub> /64 (From prescaler)                  |

| 1    | 0    | 0    | clk <sub>NO</sub> /256 (From prescaler)                 |

| 1    | 0    | 1    | clk <sub>NO</sub> /1024 (From prescaler)                |

| 1    | 1    | 0    | External clock source on T0 pin. Clock on falling edge. |

| 1    | - 1  | 1    | External clock source on T0 pin. Clock on rising edge.  |

If external pin modes are used for the Timer/Counter0, transitions on the T0 pin will clock the counter even if the pin is configured as an output. This feature allows software control of the counting.

000 to stop

|   | Mode | WGM02 | WGM01 | WGM00 | Timer/Counter<br>Mode of<br>Operation | ТОР  | Update of OCRx at | TOV Flag<br>Set on <sup>(1)(2)</sup> |

|---|------|-------|-------|-------|---------------------------------------|------|-------------------|--------------------------------------|

| Γ | 0    | 0     | 0     | 0     | Normal                                | 0xFF | Immediate         | MAX                                  |

|   | 1    | 0     | 0     | 1     | PWM, Phase<br>Correct                 | 0xFF | TOP               | воттом                               |

| Γ | 2    | 0     | 1     | 0     | стс                                   | OCRA | Immediate         | MAX                                  |

|   | 3    | 0     | 1     | 1     | Fast PWM                              | 0xFF | воттом            | MAX                                  |

| f | 4    | 1     | 0     | 0     | Reserved                              | -    | -                 | -                                    |

|   | 5    | 1     | 0     | 1     | PWM, Phase<br>Correct                 | OCRA | TOP               | воттом                               |

| I | 6    | 1     | 1     | 0     | Reserved                              | _    |                   |                                      |

| Ì | 7    | 1     | 1     | 1     | Fast PWM                              | OCRA | воттом            | TOP                                  |

2 ROTTOM = 0x01

| Mode | WGM02 | WGM01 | WGM00 | Timer/Counter<br>Mode of<br>Operation | TOP  | Update of OCRx at | TOV Flag<br>Set on <sup>(1)(2</sup> |

|------|-------|-------|-------|---------------------------------------|------|-------------------|-------------------------------------|

| 0    | 0     | 0     | 0     | Normal                                | 0xFF | Immediate         | MAX                                 |

| 1    | 0     | 0     | 1     | PWM, Phase<br>Correct                 | 0xFF | TOP               | воттом                              |

| 2    | 0     | 1     | 0     | стс                                   | OCRA | Immediate         | MAX                                 |

| 3    | 0     | 1     | 1     | Fast PWM                              | 0xFF | воттом            | MAX                                 |

| 4    | 1     | 0     | 0     | Reserved                              | -    | -                 | -                                   |

| 5    | 1     | 0     | 1     | PWM, Phase<br>Correct                 | OCRA | TOP               | воттом                              |

| 6    | - 1   | 1     | 0     | Reserved                              | -    | _                 | -                                   |

| 7    | 1     | 1     | 1     | Fast PWM                              | OCRA | воттом            | TOP                                 |

Mode 3 -independent duty cycle outputs on OC0A, OC0B

| Mode | WGM02 | WGM01 | WGM00 | Timer/Counter<br>Mode of<br>Operation | ТОР  | Update of OCRx at | TOV Flag<br>Set on <sup>(1)(2</sup> |

|------|-------|-------|-------|---------------------------------------|------|-------------------|-------------------------------------|

| 0    | 0     | 0     | 0     | Normal                                | 0xFF | Immediate         | MAX                                 |

| 1    | 0     | 0     | 1     | PWM, Phase<br>Correct                 | 0xFF | TOP               | воттом                              |

| 2    | 0     | 1     | 0     | стс                                   | OCRA | Immediate         | MAX                                 |

| 3    | 0     | 1     | 1     | Fast PWM                              | 0xFF | воттом            | MAX                                 |

| 4    | 1     | 0     | 0     | Reserved                              | -    | -                 | -                                   |

| 5    | 1     | 0     | 1     | PWM, Phase<br>Correct                 | OCRA | TOP               | воттом                              |

| 6    | - 1   | 1     | 0     | Reserved                              | _    |                   | _                                   |

| 7    | 1     | 1     | 1     | Fast PWM                              | OCRA | воттом            | TOP                                 |

Mode 3 -independent duty cycle outputs on OC0A, OC0B Mode 7 - square wave on OC0A; PWM output on OC0B

# Timer0 OC0A modes (fast PWM)

# Timer0 OC0A modes (fast PWM)

Table 15-2. Compare Output Mode, non-PWM Mode

| COM0A1 | COM0A0 | Description                               |

|--------|--------|-------------------------------------------|

| 0      | 0      | Normal port operation, OC0A disconnected. |

| 0      | 1      | Toggle OC0A on Compare Match              |

| 1      | 0      | Clear OC0A on Compare Match               |

| 1      | 1      | Set OC0A on Compare Match                 |

Table 15-3 shows the COM0A1:0 bit functionality when the WGM01:0 bits are set to fast PWM mode.

Table 15-3. Compare Output Mode, Fast PWM Mode(1)

| COM0A1 | COM0A0 | Description                                                                                   |

|--------|--------|-----------------------------------------------------------------------------------------------|

| 0      | 0      | Normal port operation, OC0A disconnected.                                                     |

| 0      | 1      | WGM02 = 0: Normal Port Operation, OC0A Disconnected. WGM02 = 1: Toggle OC0A on Compare Match. |

| 1      | 0      | Clear OC0A on Compare Match, set OC0A at BOTTOM, (non-inverting mode).                        |

| 1      | 1      | Set OCOA on Compare Match, clear OCOA at BOTTOM, (inverting mode).                            |

Note: 1. A special case occurs when OCR0A equals TOP and COM0A1 is set. In this case, the Compare Match is ignored, but the set or clear is done at BOTTOM, See "Fast PWM Mode" on page 99 for more details,

Table 15-4 shows the COM0A1:0 bit functionality when the WGM02:0 bits are set to phase correct PWM mode.

## Timer0 OC0A modes (fast PWM)

Table 15-2. Compare Output Mode, non-PWM Mode

| COM0A1 | COM0A0 | Description                               |

|--------|--------|-------------------------------------------|

| 0      | 0      | Normal port operation, OC0A disconnected. |

| 0      | 1      | Toggle OC0A on Compare Match              |

| 1      | 0      | Clear OC0A on Compare Match               |

| 1      | 1      | Set OC0A on Compare Match                 |

Table 15-3 shows the COM0A1:0 bit functionality when the WGM01:0 bits are set to fast PWM mode.

Table 15-3. Compare Output Mode, Fast PWM Mode(1)

| COM0A1 | Description |                                                                                                  |

|--------|-------------|--------------------------------------------------------------------------------------------------|

| 0 0    |             | Normal port operation, OC0A disconnected.                                                        |

| 0      | 1           | WGM02 = 0: Normal Port Operation, OC0A Disconnected.<br>WGM02 = 1: Toggle OC0A on Compare Match. |

| 1      | 0           | Clear OC0A on Compare Match, set OC0A at BOTTOM, (non-inverting mode).                           |

| 1      | 1           | Set OCOA on Compare Match, clear OCOA at BOTTOM, (inverting mode).                               |

Note: 1. A special case occurs when OCR0A equals TOP and COM0A1 is set. In this case, the Compare Match is ignored, but the set or clear is done at BOTTOM, See "Fast PWM Mode" on page 99 for more details.

Table 15-4 shows the COM0A1:0 bit functionality when the WGM02:0 bits are set to phase correct PWM mode.

#### Note 01 operation

# Timer0 OC0B modes (fast PWM)

## Timer0 OC0B modes (fast PWM)

Table 15-5. Compare Output Mode, non-PWM Mode

| COM0B | COM0B0 | Description                               |

|-------|--------|-------------------------------------------|

| 0     | 0      | Normal port operation, OC0B disconnected. |

| 0     | 1      | Toggle OC0B on Compare Match              |

| 1     | 0      | Clear OC0B on Compare Match               |

| 1     | 1      | Set OC0B on Compare Match                 |

Table 15-6 shows the COM0B1:0 bit functionality when the WGM02:0 bits are set to fast PWM mode.

Table 15-6. Compare Output Mode, Fast PWM Mode(1)

| COM0B1 | COM0B0 | Description                                                           |

|--------|--------|-----------------------------------------------------------------------|

| 0      | 0      | Normal port operation, OC0B disconnected.                             |

| 0      | 1      | Reserved                                                              |

| 1      | 0      | Clear OC0B on Compare Match, set OC0B at BOTTOM, (non-inverting mode) |

| 1      | 1      | Set OC0B on Compare Match, clear OC0B at BOTTOM, (inverting mode).    |

Note: 1. A special case occurs when OCR0B equals TOP and COM0B1 is set. In this case, the Compare Match is ignored, but the set or clear is done at TOP. See "Fast PWM Mode" on page 99 for more details.

Table 15-7 shows the COM0B1:0 bit functionality when the WGM02:0 bits are set to phase correct PWM mode.

## Timer0 OC0B modes (fast PWM)

Table 15-5. Compare Output Mode, non-PWM Mode

| COM0B1 | COM0B0 | Description                               |

|--------|--------|-------------------------------------------|

| 0      | 0      | Normal port operation, OC0B disconnected. |

| 0      | 1      | Toggle OC0B on Compare Match              |

| 1      | 0      | Clear OC0B on Compare Match               |

| 1      | 1      | Set OC0B on Compare Match                 |

Table 15-6 shows the COM0B1:0 bit functionality when the WGM02:0 bits are set to fast PWM mode.

Table 15-6. Compare Output Mode, Fast PWM Mode(1)

| COM0B1 | COM0B0 | Description                                                           |

|--------|--------|-----------------------------------------------------------------------|

| 0      | 0      | Normal port operation, OC0B disconnected.                             |

| 0      | 1      | Reserved                                                              |

| 1      | 0      | Clear OC0B on Compare Match, set OC0B at BOTTOM, (non-inverting mode) |

| 1      | 1      | Set OCOB on Compare Match, clear OCOB at BOTTOM,<br>(inverting mode). |

Note: 1. A special case occurs when OCR0B equals TOP and COM0B1 is set. In this case, the Compare Match is ignored, but the set or clear is done at TOP. See "Fast PWM Mode" on page 99 for more details.

Table 15-7 shows the COM0B1:0 bit functionality when the WGM02:0 bits are set to phase correct PWM mode.

Note 10 operation; 11 output is inverted

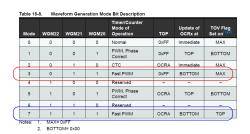

|   | Table 15- | 8. Wave | form Gener | ation Mode | Bit Description                       |      |                   |                                      |

|---|-----------|---------|------------|------------|---------------------------------------|------|-------------------|--------------------------------------|

|   | Mode      | WGM02   | WGM01      | WGM00      | Timer/Counter<br>Mode of<br>Operation | ТОР  | Update of OCRx at | TOV Flag<br>Set on <sup>(1)(2)</sup> |

|   | 0         | 0       | 0          | 0          | Normal                                | 0xFF | Immediate         | MAX                                  |

| ( | 1         | 0       | 0          | 1          | PWM, Phase<br>Correct                 | 0xFF | TOP               | воттом                               |

|   | 2         | 0       | 1          | 0          | стс                                   | OCRA | Immediate         | MAX                                  |

|   | 3         | 0       | 1          | 1          | Fast PWM                              | 0xFF | воттом            | MAX                                  |

|   | 4         | 1       | 0          | 0          | Reserved                              | -    | -                 | -                                    |

| ( | 5         | 1       | 0          | 1          | PWM, Phase<br>Correct                 | OCRA | TOP               | воттом                               |

|   | 6         | 1       | 1          | 0          | Reserved                              | -    | -                 |                                      |

|   | 7         | 1       | 1          | 1          | Fast PWM                              | OCRA | воттом            | TOP                                  |

1. MAX = UXFF

2. BOTTOM = 0x0f

|   | Mode | WGM02 | WGM01 | WGM00 | Timer/Counter<br>Mode of<br>Operation | ТОР  | Update of OCRx at | TOV Flag<br>Set on <sup>(1)(2)</sup> |

|---|------|-------|-------|-------|---------------------------------------|------|-------------------|--------------------------------------|

|   | 0    | 0     | 0     | 0     | Normal                                | 0xFF | Immediate         | MAX                                  |

|   | 1    | 0     | 0     | 1     | PWM, Phase<br>Correct                 | 0xFF | TOP               | воттом                               |

| ` | 2    | 0     | 1     | 0     | стс                                   | OCRA | Immediate         | MAX                                  |

|   | 3    | 0     | 1     | 1     | Fast PWM                              | 0xFF | BOTTOM            | MAX                                  |

|   | 4    | - 1   | 0     | 0     | Reserved                              | -    | -                 | -                                    |

| 1 | 5    | 1     | 0     | 1     | PWM, Phase<br>Correct                 | OCRA | TOP               | воттом                               |

| Ì | 6    | - 1   | 1     | 0     | Reserved                              | -    | -                 | -                                    |

|   | 7    | 1     | 1     | 1     | Fast PWM                              | OCRA | воттом            | TOP                                  |

Mode 1 -independent duty cycle outputs on OC0A, OC0B

BOTTOM = 0x00

| Mode | WGM02 | WGM01 | WGM00 | Timer/Counter<br>Mode of<br>Operation | ТОР  | Update of OCRx at | TOV Flag<br>Set on <sup>(1)(2</sup> |

|------|-------|-------|-------|---------------------------------------|------|-------------------|-------------------------------------|

| 0    | 0     | 0     | 0     | Normal                                | 0xFF | Immediate         | MAX                                 |

| 1    | 0     | 0     | 1     | PWM, Phase<br>Correct                 | 0xFF | TOP               | воттом                              |

| 2    | 0     | 1     | 0     | стс                                   | OCRA | Immediate         | MAX                                 |

| 3    | 0     | 1     | 1     | Fast PWM                              | 0xFF | воттом            | MAX                                 |

| 4    | 1     | 0     | 0     | Reserved                              | -    | -                 | -                                   |

| 5    | 1     | 0     | 1     | PWM, Phase<br>Correct                 | OCRA | TOP               | воттом                              |

| 6    | - 1   | - 1   | 0     | Reserved                              | -    | -                 | -                                   |

| 7    | 1     | 1     | 1     | Fast PWM                              | OCRA | воттом            | TOP                                 |

Mode 1 -independent duty cycle outputs on OC0A, OC0B Mode 5 - square wave on OC0A; PWM output on OC0B

# Timer0 OC0A modes (phase correct PWM)

# Timer0 OC0A modes (phase correct PWM)

Table 15-4. Compare Output Mode, Phase Correct PWM Mode<sup>(1)</sup>

| COM0A1 | COM0A0 | Description                                                                                   |

|--------|--------|-----------------------------------------------------------------------------------------------|

| 0      | 0      | Normal port operation, OC0A disconnected.                                                     |

| 0      | 1      | WGM02 = 0: Normal Port Operation, OC0A Disconnected. WGM02 = 1: Toggle OC0A on Compare Match. |

| 1      | 0      | Clear OC0A on Compare Match when up-counting. Set OC0A on Compare Match when down-counting.   |

| 1      | 1      | Set OC0A on Compare Match when up-counting, Clear OC0A on Compare Match when down-counting.   |

Note: 1. A special case occurs when OCR0A equals TOP and COM0A1 is set. In this case, the Compare Match is ignored, but the set or clear is done at TOP. See "Phase Correct PWM Mode" on page 125 for more details.

## Timer0 OC0A modes (phase correct PWM)

| Table 15-4. Compare Output Mode, Phase Correct PWM Mode <sup>(1)</sup> |   |                                                                                                  |  |  |

|------------------------------------------------------------------------|---|--------------------------------------------------------------------------------------------------|--|--|

| COM0A1 COM0A0 Description                                              |   | Description                                                                                      |  |  |

| 0                                                                      | 0 | Normal port operation, OC0A disconnected.                                                        |  |  |

| 0                                                                      | 1 | WGM02 = 0: Normal Port Operation, OC0A Disconnected.<br>WGM02 = 1: Toggle OC0A on Compare Match. |  |  |

| 1                                                                      | 0 | Clear OC0A on Compare Match when up-counting. Set OC0A on Compare Match when down-counting.      |  |  |

| 1                                                                      | 1 | Set OCOA on Compare Match when up-counting, Clear OCOA on Compare Match when down-counting.      |  |  |

Note: 1. A special case occurs when OCR0A equals TOP and COM0A1 is set. In this case, the Compare Match is ignored, but the set or clear is done at TOP. See "Phase Correct PWM Mode" on page 125 for more details.

Note 01 operation

## Timer0 OC0B modes (phase correct PWM)

## Timer0 OC0B modes (phase correct PWM)

Table 15-7. Compare Output Mode, Phase Correct PWM Mode<sup>(1)</sup>

| COM0B1 | COM0B0 | Description                                                                                 |  |

|--------|--------|---------------------------------------------------------------------------------------------|--|

| 0      | 0      | Normal port operation, OC0B disconnected.                                                   |  |

| 0      | 1      | Reserved                                                                                    |  |

| 1      | 0      | Clear OCOB on Compare Match when up-counting, Set OCOB of Compare Match when down-counting. |  |

| 1      | 1      | Set OCOB on Compare Match when up-counting. Clear OCOB on Compare Match when down-counting. |  |

Note: 1. A special case occurs when OCR0B equals TOP and COM0B1 is set. In this case, the Compare Match is ignored, but the set or clear is done at TOP. See "Phase Correct PWM Mode" on page 100 for more details.

### Timer0 OC0B modes (phase correct PWM)

Note: 1. A special case occurs when OCR0B equals TOP and COM0B1 is set. In this case, the Compare Match is ignored, but the set or clear is done at TOP. See "Phase Correct PWM Mode" on page 100 for more details.

Note 10 operation; 11 output is inverted

BOTTOM

BOTTOM

$0 \times 00$

BOTTOM

0×00

MAX

BOTTOM

$0 \times 00$

MAX

0xFF

BOTTOM

0x00

MAX

0xFF

maximum value the timer can reach

BOTTOM

$0 \times 00$

MAX

0xFF

maximum value the timer can reach

TOP

BOTTOM

$0 \times 00$

MAX

0xFF

maximum value the timer can reach

TOP

MAX or value in OCR2A, depending on mode

#### Timer2 prescaler

## Timer2 prescaler

Table 18-9. Clock Select Bit Description

| CS22 | CS21 | CS20 | Description                               |

|------|------|------|-------------------------------------------|

| 0    | 0    | 0    | No clock source (Timer/Counter stopped).  |

| 0    | 0    | 1    | clk <sub>T2S</sub> /(No prescaling)       |

| 0    | 1    | 0    | clk <sub>T2S</sub> /8 (From prescaler)    |

| 0    | 1    | 1    | clk <sub>T2S</sub> /32 (From prescaler)   |

| 1    | 0    | 0    | clk <sub>T2S</sub> /64 (From prescaler)   |

| 1    | 0    | 1    | clk <sub>T2S</sub> /128 (From prescaler)  |

| 1    | 1    | 0    | clk <sub>T2S</sub> /256 (From prescaler)  |

| 1    | 1    | 1    | clk <sub>T2S</sub> /1024 (From prescaler) |

If external pin modes are used for the Timer/Counter0, transitions on the T0 pin will clock the counter even if the pin is configured as an output. This feature allows software control of the counting.

### Timer2 prescaler

Table 18-9. Clock Select Bit Description

| CS22 | CS21 | CS20 | Description                               |

|------|------|------|-------------------------------------------|

| 0    | 0    | 0    | No clock source (Timer/Counter stopped).  |

| 0    | 0    | 1    | clk <sub>T2S</sub> /(No prescaling)       |

| 0    | 1    | 0    | clk <sub>T2S</sub> /8 (From prescaler)    |

| 0    | 1    | 1    | clk <sub>T2S</sub> /32 (From prescaler)   |

| 1    | 0    | 0    | clk <sub>T2S</sub> /64 (From prescaler)   |

| 1    | 0    | 1    | clk <sub>T2S</sub> /128 (From prescaler)  |

| 1    | 1    | 0    | clk <sub>T2S</sub> /256 (From prescaler)  |

| 1    | 1    | 1    | clk <sub>T2S</sub> /1024 (From prescaler) |

If external pin modes are used for the Timer/Counter0, transitions on the T0 pin will clock the counter even if the pin is configured as an output. This feature allows software control of the counting.

000 to stop

Mode 3 -independent duty cycle outputs on OC2A, OC2B

| Mode | WGM22 | WGM21 | WGM20 | Timer/Counter<br>Mode of<br>Operation | ТОР  | Update of OCRx at | TOV Flag<br>Set on <sup>(1)</sup> |

|------|-------|-------|-------|---------------------------------------|------|-------------------|-----------------------------------|

| 0    | 0     | 0     | 0     | Normal                                | 0xFF | Immediate         | MAX                               |

| 1    | 0     | 0     | 1     | PWM, Phase<br>Correct                 | 0xFF | ТОР               | воттом                            |

| 2    | 0     | - 1   | 0     | стс                                   | OCRA | Immediate         | MAX                               |

| 3    | 0     | 1     | 1     | Fast PWM                              | 0xFF | воттом            | MAX                               |

| 4    | - 1   | 0     | 0     | Reserved                              | -    | -                 |                                   |

| 5    | 1     | 0     | 1     | PWM, Phase<br>Correct                 | OCRA | ТОР               | воттом                            |

| 6    | - 1   | 1     | 0     | Reserved                              | _    | _                 |                                   |

| 7    | 1     | 1     | 1     | Fast PWM                              | OCRA | воттом            | TOP                               |

Mode 3 -independent duty cycle outputs on OC2A, OC2B Mode 7 - square wave on OC2A; PWM output on OC2B

## Timer2 OC2A modes (fast PWM)

## Timer2 OC2A modes (fast PWM)

Table 18-2. Compare Output Mode, non-PWM Mode

| COM2A1 | COM2A0 | Description                               |  |

|--------|--------|-------------------------------------------|--|

| 0      | 0      | Normal port operation, OC0A disconnected. |  |

| 0      | 1      | Toggle OC2A on Compare Match              |  |

| 1      | 0      | Clear OC2A on Compare Match               |  |

| 1      | 1      | Set OC2A on Compare Match                 |  |

Table 18-3 shows the COM2A1:0 bit functionality when the WGM21:0 bits are set to fast PWM mode.

Table 18-3. Compare Output Mode, Fast PWM Mode<sup>(1)</sup>

| COM2A1 | COM2A0 | Description                                                                                   |  |  |

|--------|--------|-----------------------------------------------------------------------------------------------|--|--|

| 0 0    |        | Normal port operation, OC2A disconnected.                                                     |  |  |

| 0      | 1      | WGM22 = 0: Normal Port Operation, OC0A Disconnected. WGM22 = 1: Toggle OC2A on Compare Match. |  |  |

| 1      | 0      | Clear OC2A on Compare Match, set OC2A at BOTTOM, (non-inverting mode).                        |  |  |

| 1      | 1      | Set OC2A on Compare Match, clear OC2A at BOTTOM, (inverting mode).                            |  |  |

Note: 1. A special case occurs when OCR2A equals TOP and COM2A1 is set. In this case, the Compare Match is ignored, but the set or clear is done at BOTTOM. See "Fast PWM Mode" on page 147 for more details.

## Timer2 OC2A modes (fast PWM)

Table 18-2. Compare Output Mode, non-PWM Mode

| COM2A | 1 COM2A0 | Description                               |  |

|-------|----------|-------------------------------------------|--|

| 0     | 0        | Normal port operation, OC0A disconnected. |  |

| 0     | 1        | Toggle OC2A on Compare Match              |  |

| 1     | 0        | Clear OC2A on Compare Match               |  |

| 1     | 1        | Set OC2A on Compare Match                 |  |

Table 18-3 shows the COM2A1:0 bit functionality when the WGM21:0 bits are set to fast PWM mode.

Table 18-3. Compare Output Mode, Fast PWM Mode (1)

| COM2A1 COM2A0 |   | Description                                                                                   |

|---------------|---|-----------------------------------------------------------------------------------------------|

| 0 0           |   | Normal port operation, OC2A disconnected.                                                     |

| 0             | 1 | WGM22 = 0: Normal Port Operation, OC0A Disconnected. WGM22 = 1: Toggle OC2A on Compare Match. |

| 1             | 0 | Clear OC2A on Compare Match, set OC2A at BOTTOM, (non-inverting mode).                        |

| 1             | 1 | Set OC2A on Compare Match, clear OC2A at BOTTOM, (inverting mode).                            |

Note: 1. A special case occurs when OCR2A equals TOP and COM2A1 is set. In this case, the Compare Match is ignored, but the set or clear is done at BOTTOM. See "Fast PWM Mode" on page 147 for more details.

Note 01 operation

### Timer2 OC2B modes (fast PWM)

### Timer2 OC2B modes (fast PWM)

Table 18-5. Compare Output Mode, non-PWM Mode

| COM2B1 | COM2B0 | Description                               |

|--------|--------|-------------------------------------------|

| 0      | 0      | Normal port operation, OC2B disconnected. |

| 0      | 1      | Toggle OC2B on Compare Match              |

| 1      | 0      | Clear OC2B on Compare Match               |

| 1      | 1      | Set OC2B on Compare Match                 |

Table 18-6 shows the COM2B1:0 bit functionality when the WGM22:0 bits are set to fast PWM mode.

Table 18-6. Compare Output Mode, Fast PWM Mode<sup>(1)</sup>

| COM2B1 | COM2B0 | Description                                                            |  |  |

|--------|--------|------------------------------------------------------------------------|--|--|

| 0      | 0      | Normal port operation, OC2B disconnected.                              |  |  |

| 0      | 1      | Reserved                                                               |  |  |

| 1      | 0      | Clear OC2B on Compare Match, set OC2B at BOTTOM, (non-inverting mode). |  |  |

| 1      | 1      | Set OC2B on Compare Match, clear OC2B at BOTTOM,<br>(inverting mode),  |  |  |

Note: 1. A special case occurs when OCR2B equals TOP and COM2B1 is set. In this case, the Compare Match is ignored, but the set or clear is done at BOTTOM. See "Phase Correct PWM Mode" on page 148 for more details.

## Timer2 OC2B modes (fast PWM)

| COM2B1 | COM2B0 | Description                               |

|--------|--------|-------------------------------------------|

| 0      | 0      | Normal port operation, OC2B disconnected. |

| 0      | 1      | Toggle OC2B on Compare Match              |

| 1      | 0      | Clear OC2B on Compare Match               |

| 1      | 1      | Set OC2B on Compare Match                 |

Table 18-6 shows the COM2B1:0 bit functionality when the WGM22:0 bits are set to fast PWM mode.

Table 18-6. Compare Output Mode, Fast PWM Mode(1)

| COM2B1 | COM2B0 | Description                                                            |

|--------|--------|------------------------------------------------------------------------|

| 0      | 0      | Normal port operation, OC2B disconnected.                              |

| 0      | 1      | Reserved                                                               |

| 1      | 0      | Clear OC2B on Compare Match, set OC2B at BOTTOM, (non-inverting mode). |

| 1      | 1      | Set OC2B on Compare Match, clear OC2B at BOTTOM,                       |

Note: 1. A special case occurs when OCR2B equals TOP and COM2B1 is set. In this case, the Compare Match is ignored, but the set or clear is done at BOTTOM. See "Phase Correct PWM Mode" on page 148 for more ideals."

Note 10 operation; 11 output is inverted

Details Timer0 Timer2

#### Timer2 waveform selection

Table 18-8. Waveform Generation Mode Bit Description

|   | Mode | WGM22 | WGM21 | WGM20 | Timer/Counter<br>Mode of<br>Operation | ТОР  | Update of OCRx at | TOV Flag<br>Set on <sup>(1)(2)</sup> |

|---|------|-------|-------|-------|---------------------------------------|------|-------------------|--------------------------------------|

|   | 0    | 0     | 0     | 0     | Normal                                | 0xFF | Immediate         | MAX                                  |

|   | 1    | 0     | 0     | 1     | PWM, Phase<br>Correct                 | 0xFF | TOP               | воттом                               |

| Ì | 2    | 0     | 1     | 0     | стс                                   | OCRA | Immediate         | MAX                                  |

|   | 3    | 0     | 1     | 1     | Fast PWM                              | 0xFF | воттом            | MAX                                  |

|   | 4    | 1     | 0     | 0     | Reserved                              | -    | -                 | -                                    |

| ( | 5    | 1     | 0     | 1     | PWM, Phase<br>Correct                 | OCRA | TOP               | воттом                               |

| 1 | 6    | 1     | 1     | 0     | Reserved                              | -    | -                 | -                                    |

|   | 7    | 1     | 1     | 1     | Fast PWM                              | OCRA | воттом            | TOP                                  |

Notes: 1. MAX= 0xFF 2. BOTTOM= 0x00

|   | Mode | WGM22 | WGM21 | WGM20 | Timer/Counter<br>Mode of<br>Operation | тор  | Update of OCRx at | TOV Flag<br>Set on <sup>(1)(2)</sup> |

|---|------|-------|-------|-------|---------------------------------------|------|-------------------|--------------------------------------|

|   | 0    | 0     | 0     | 0     | Normal                                | 0xFF | Immediate         | MAX                                  |

|   | 1    | 0     | 0     | 1     | PWM, Phase<br>Correct                 | 0xFF | TOP               | воттом                               |

| ` | 2    | 0     | 1     | 0     | стс                                   | OCRA | Immediate         | MAX                                  |

|   | 3    | 0     | 1     | 1     | Fast PWM                              | 0xFF | воттом            | MAX                                  |

|   | 4    | 1     | 0     | 0     | Reserved                              | -    | -                 | -                                    |

|   | 5    | 1     | 0     | 1     | PWM, Phase<br>Correct                 | OCRA | TOP               | воттом                               |

| ` | 6    | 1     | 1     | 0     | Reserved                              | -    | -                 | -                                    |

|   | 7    | 1     | 1     | 1     | Fast PWM                              | OCRA | воттом            | TOP                                  |

Mode 1 -independent duty cycle outputs on OC2A, OC2B

2. BOTTOM= 0x00

|   | Mode | WGM22 | WGM21 | WGM20 | Timer/Counter<br>Mode of<br>Operation | ТОР  | Update of OCRx at | TOV Flag<br>Set on <sup>(1)(2)</sup> |

|---|------|-------|-------|-------|---------------------------------------|------|-------------------|--------------------------------------|

|   | 0    | 0     | 0     | 0     | Normal                                | 0xFF | Immediate         | MAX                                  |

|   | 1    | 0     | 0     | 1     | PWM, Phase<br>Correct                 | 0xFF | TOP               | воттом                               |

| Г | 2    | 0     | 1     | 0     | стс                                   | OCRA | Immediate         | MAX                                  |

|   | 3    | 0     | 1     | - 1   | Fast PWM                              | 0xFF | воттом            | MAX                                  |

|   | 4    | 1     | 0     | 0     | Reserved                              | -    | -                 | -                                    |

|   | 5    | 1     | 0     | 1     | PWM, Phase<br>Correct                 | OCRA | TOP               | воттом                               |

| Г | 6    | 1     | 1     | 0     | Reserved                              | -    | -                 | -                                    |

|   | 7    | 1     | 1     | 1     | Fast PWM                              | OCRA | воттом            | TOP                                  |

Mode 1 -independent duty cycle outputs on OC2A, OC2B Mode 5 - square wave on OC2A; PWM output on OC2B

# Timer2 OC2A modes (phase correct PWM)

# Timer2 OC2A modes (phase correct PWM)

Table 18-4. Compare Output Mode, Phase Correct PWM Mode<sup>(1)</sup>

| COM2A1 | COM2A0 | Description                                                                                      |

|--------|--------|--------------------------------------------------------------------------------------------------|

| 0      | 0      | Normal port operation, OC2A disconnected.                                                        |

| 0      | 1      | WGM22 = 0; Normal Port Operation, OC2A Disconnected.<br>WGM22 = 1; Toggle OC2A on Compare Match. |

| 1      | 0      | Clear OC2A on Compare Match when up-counting. Set OC2A on Compare Match when down-counting.      |

| 1      | 1      | Set OC2A on Compare Match when up-counting. Clear OC2A on Compare Match when down-counting.      |

Note: 1. A special case occurs when OCR2A equals TOP and COM2A1 is set. In this case, the Compare Match is ignored, but the set or clear is done at TOP. See "Phase Correct PWM Mode" on page 148 for more details.

### Timer2 OC2A modes (phase correct PWM)

| Table 18-4. | ut Mode, Phase Correct PWM Mode <sup>(1)</sup> |                                                                                                  |

|-------------|------------------------------------------------|--------------------------------------------------------------------------------------------------|

| COM2A1      | COM2A0                                         | Description                                                                                      |

| 0           | 0                                              | Normal port operation, OC2A disconnected.                                                        |

| 0           | 1                                              | WGM22 = 0: Normal Port Operation, OC2A Disconnected.<br>WGM22 = 1: Toggle OC2A on Compare Match. |

| 1           | 0                                              | Clear OC2A on Compare Match when up-counting. Set OC2A on Compare Match when down-counting.      |

| 1           | 1                                              | Set OC2A on Compare Match when up-counting. Clear OC2A on Compare Match when down-counting.      |

Note: 1. A special case occurs when OCR2A equals TOP and COM2A1 is set. In this case, the Compare Match is ignored, but the set or clear is done at TOP. See "Phase Correct PWM Mode" on page 148 for more details.

Note 01 operation

### Timer2 OC2B modes (phase correct PWM)

# Timer2 OC2B modes (phase correct PWM)

Table 18-7. Compare Output Mode, Phase Correct PWM Mode(1)

| COM2B1 | 1 COM2B0 Description |                                                                                             |

|--------|----------------------|---------------------------------------------------------------------------------------------|

| 0      | 0                    | Normal port operation, OC2B disconnected.                                                   |

| 0      | 1                    | Reserved                                                                                    |

| 1      | 0                    | Clear OC2B on Compare Match when up-counting. Set OC2B on Compare Match when down-counting. |

| 1      | 1                    | Set OC2B on Compare Match when up-counting, Clear OC2B on Compare Match when down-counting. |

A special case occurs when OCR2B equals TOP and COM2B1 is set. In this case, the Compare Match is ignored, but the set or clear is done at TOP. See "Phase Correct PWM Mode" on page 148 for more details.

### Timer2 OC2B modes (phase correct PWM)

Table 18-7. Compare Output Mode, Phase Correct PWM Mode<sup>(1)</sup>

| COM2B1 | COM2B0 | Description                                                                                 |

|--------|--------|---------------------------------------------------------------------------------------------|

| 0      | 0      | Normal port operation, OC2B disconnected.                                                   |

| 0 1    |        | Reserved                                                                                    |

| 1      | 0      | Clear OC2B on Compare Match when up-counting. Set OC2B on Compare Match when down-counting. |

| 1      | 1      | Set OC2B on Compare Match when up-counting. Clear OC2B on Compare Match when down-counting. |

Note: 1. A special case occurs when OCR2B equals TOP and COM2B1 is set. In this case, the Compare Match is ignored, but the set or clear is done at TOP. See "Phase Correct PWM Mode" on page 148 for more details.

Note 10 operation; 11 output is inverted