# CP316 Interrupts

Terry Sturtevant

Wilfrid Laurier University

February 6, 2018

Introduction Initialization Service Fast register Stack Rules for Interrupts

### Introduction to Interrupts

Interrupts allow program control to change due to events.

Interrupts allow program control to change due to *events*. **Interrupt vectors** are program locations

Interrupts allow program control to change due to *events*.

Interrupt vectors are program locations

where interrupt service routines are located.

Interrupts allow program control to change due to events.

**Interrupt vectors** are program locations

where interrupt service routines are located.

After interrupt service, the program control returns to original.

Interrupts allow program control to change due to events.

**Interrupt vectors** are program locations

where interrupt service routines are located.

After interrupt service, the program control returns to original.

The PIC has 2 interrupt **priority levels**,

Interrupts allow program control to change due to *events*.

Interrupt vectors are program locations

where interrupt service routines are located.

After interrupt service, the program control returns to original.

The PIC has 2 interrupt **priority levels**,

high and low.

Interrupts allow program control to change due to events.

**Interrupt vectors** are program locations

where interrupt service routines are located.

After interrupt service, the program control returns to original.

The PIC has 2 interrupt **priority levels**,

high and low.

A high priority interrupt can happen *during* a low priority interrupt, but not the other way around.

Introduction Initialization Service Fast register Stack Rules for Interrupts

# Terminology

Enabled/Disabled

Enabled/Disabled

whether a specific event will generate an interrupt

- Enabled/Disabled whether a specific event will generate an interrupt

- Pending

- Enabled/Disabled whether a specific event will generate an interrupt

- Pending

whether the event has occurred

- Enabled/Disabled whether a specific event will generate an interrupt

- Pending whether the event has occurred

- Flag

- Enabled/Disabled

whether a specific event will generate an interrupt

- Pending whether the event has occurred

- Flag

bit in memory indicating an interrupt is pending

- Enabled/Disabled

whether a specific event will generate an interrupt

- Pending whether the event has occurred

- Flag

bit in memory indicating an interrupt is pending

Note: Flags are usually set whether or not corresponding interrupts are enabled.

- Enabled/Disabled

whether a specific event will generate an interrupt

- Pending whether the event has occurred

- Flag

bit in memory indicating an interrupt is pending

- Note: Flags are usually set whether or not corresponding interrupts are enabled.

- Set or Clear

- Enabled/Disabled

whether a specific event will generate an interrupt

- Pending whether the event has occurred

- Flag

bit in memory indicating an interrupt is pending

Note: Flags are usually set whether or not corresponding

interrupts are enabled.

- Set or Clear state of flag indicating pending or not

Introduction Initialization Service Fast register Stack Rules for Interrupts

## Interrupts

# Interrupts

overview

# Interrupts

overview

$\rightarrow \, \text{Section} \,\, 6.2.5$

# Interrupts

#### overview

- $\rightarrow$  Section 6.2.5

- $\rightarrow$  Section 8.0

# Interrupts

#### overview

- $\rightarrow$  Section 6.2.5

- $\rightarrow$  Section 8.0

vectors

#### overview

- $\rightarrow$  Section 6.2.5

- $\rightarrow$  Section 8.0

#### vectors

$\rightarrow$  Section 6.2.6

#### overview

- $\rightarrow$  Section 6.2.5

- $\rightarrow$  Section 8.0

#### vectors

$\rightarrow$  Section 6.2.6

priority

#### overview

- $\rightarrow$  Section 6.2.5

- $\rightarrow$  Section 8.0

#### vectors

$\rightarrow$  Section 6.2.6

### priority

$\rightarrow$  Section 6.2.4

#### overview

- $\rightarrow$  Section 6.2.5

- $\rightarrow$  Section 8.0

#### vectors

$\rightarrow$  Section 6.2.6

### priority

$\rightarrow$  Section 6.2.4

status; clear, pending

#### overview

- $\rightarrow$  Section 6.2.5

- $\rightarrow$  Section 8.0

#### vectors

$\rightarrow$  Section 6.2.6

### priority

$\rightarrow$  Section 6.2.4

status; clear, pending

$\rightarrow$  Sections 6.2.3

#### overview

- $\rightarrow$  Section 6.2.5

- $\rightarrow$  Section 8.0

#### vectors

$\rightarrow$  Section 6.2.6

### priority

$\rightarrow$  Section 6.2.4

status; clear, pending

$\rightarrow$  Sections 6.2.3

bits; enable, priority, flag

#### overview

- $\rightarrow$  Section 6.2.5

- $\rightarrow$  Section 8.0

#### vectors

$\rightarrow$  Section 6.2.6

### priority

$\rightarrow$  Section 6.2.4

status; clear, pending

$\rightarrow$  Sections 6.2.3

bits; enable, priority, flag

$\rightarrow$  Sections 6.4.2

Here's a code fragment from a typical program:

Here's a code fragment from a typical program:

```

;;; vectors

org 0x0000 ; reset vector

goto start

; beginning of program

org 0x0008; high priority int. vector

goto high_ISR; program memory label

goto $

:none for now

0 \times 0018

; low priority int. vector

org

goto $

:none for now

goto low_ISR

```

# Interrupt Initialization

# Interrupt Initialization

The *sequence* of initializing interrupts is important.

# Interrupt Initialization

The *sequence* of initializing interrupts is important.

• enable priority (RCON)

The *sequence* of initializing interrupts is important.

enable priority (RCON)unless you need compatibility with older devices

- enable priority (RCON)unless you need compatibility with older devices

- configure individual interrupt sources (various registers)

- enable priority (RCON) unless you need compatibility with older devices

- configure individual interrupt sources (various registers) any needed configuration, initialization of variables, etc.

- enable priority (RCON) unless you need compatibility with older devices

- configure individual interrupt sources (various registers) any needed configuration, initialization of variables, etc.

- clear flags (various registers)

- enable priority (RCON) unless you need compatibility with older devices

- configure individual interrupt sources (various registers) any needed configuration, initialization of variables, etc.

- On reset, many interrupt flags are in an unknown state, so interrupts may be incorrectly identified as pending.

- enable priority (RCON) unless you need compatibility with older devices

- configure individual interrupt sources (various registers) any needed configuration, initialization of variables, etc.

- On reset, many interrupt flags are in an unknown state, so interrupts may be incorrectly identified as pending.

- enable (various registers)

- enable priority (RCON) unless you need compatibility with older devices

- configure individual interrupt sources (various registers) any needed configuration, initialization of variables, etc.

- On reset, many interrupt flags are in an unknown state, so interrupts may be incorrectly identified as pending.

- enable (various registers) for each individual source required

- enable priority (RCON) unless you need compatibility with older devices

- configure individual interrupt sources (various registers) any needed configuration, initialization of variables, etc.

- On reset, many interrupt flags are in an unknown state, so interrupts may be incorrectly identified as pending.

- enable (various registers) for each individual source required

- **global** enable all interrupts (INTCON)

- enable priority (RCON) unless you need compatibility with older devices

- configure individual interrupt sources (various registers) any needed configuration, initialization of variables, etc.

- On reset, many interrupt flags are in an unknown state, so interrupts may be incorrectly identified as pending.

- enable (various registers) for each individual source required

- global enable all interrupts (INTCON) after all individual sources have been initialized

- enable priority (RCON) unless you need compatibility with older devices

- configure individual interrupt sources (various registers) any needed configuration, initialization of variables, etc.

- clear flags (various registers) On reset, many interrupt flags are in an unknown state, so interrupts may be incorrectly identified as pending.

- enable (various registers) for each individual source required

- global enable all interrupts (INTCON) after all individual sources have been initialized needed for any interrupt service to occur

Introduction

Initialization

Service

Fast register Stack

Rules for Interrupts

Initialization

Service

Fast register Stack

Rules for Interrupt

# Example: Timer 0

• enable priority (RCON)

- enable priority (RCON)

- configure individual interrupt sources (various registers)

- enable priority (RCON)

- configure individual interrupt sources (various registers)

TMR0IP is in INTCON2

- enable priority (RCON)

- configure individual interrupt sources (various registers)

TMR0IP is in INTCON2

- clear flags (various registers)

- enable priority (RCON)

- configure individual interrupt sources (various registers)

TMR0IP is in INTCON2

- clear flags (various registers)TMR0IF is in INTCON

- enable priority (RCON)

- configure individual interrupt sources (various registers)

TMR0IP is in INTCON2

- clear flags (various registers)TMR0IF is in INTCON

- enable (various registers)

- enable priority (RCON)

- configure individual interrupt sources (various registers)

TMR0IP is in INTCON2

- clear flags (various registers)TMR0IF is in INTCON

- enable (various registers)TMR0IE is in INTCON

- enable priority (RCON)

- configure individual interrupt sources (various registers)

TMR0IP is in INTCON2

- clear flags (various registers)TMR0IF is in INTCON

- enable (various registers)

TMR0IE is in INTCON

for each individual source required

- enable priority (RCON)

- configure individual interrupt sources (various registers)

TMR0IP is in INTCON2

- clear flags (various registers)TMR0IF is in INTCON

- enable (various registers)

TMR0IE is in INTCON

for each individual source required

GIEL is in INTCON

- enable priority (RCON)

- configure individual interrupt sources (various registers)

TMR0IP is in INTCON2

- clear flags (various registers)TMR0IF is in INTCON

- enable (various registers)

TMR0IE is in INTCON

for each individual source required

GIFL is in INTCON

- **3 global** enable *all* interrupts (**INTCON**)

- enable priority (RCON)

- configure individual interrupt sources (various registers)

TMR0IP is in INTCON2

- clear flags (various registers)TMR0IF is in INTCON

- enable (various registers)

TMR0IE is in INTCON

for each individual source required

GIFL is in INTCON

- global enable all interrupts (INTCON)

GIFH is in INTCON

Introduction Initialization Service Fast register Stack Rules for Interrupts

## Interrupt Service Routines

The sequence of actions in *servicing* interrupts is also important.

The sequence of actions in *servicing* interrupts is also important.

save vital registers

The sequence of actions in *servicing* interrupts is also important.

save vital registers STATUS, BSR, WREG

The sequence of actions in *servicing* interrupts is also important.

- save vital registers STATUS, BSR, WREG

- 2 confirm source

The sequence of actions in *servicing* interrupts is also important.

- save vital registers STATUS, BSR, WREG

- 2 confirm source

Check specific flag bit to confirm that the expected source caused the interrupt.

The sequence of actions in *servicing* interrupts is also important.

- save vital registers STATUS, BSR, WREG

- Check specific flag bit to confirm that the expected source caused the interrupt.

- process

The sequence of actions in *servicing* interrupts is also important.

- save vital registers STATUS, BSR, WREG

- Check specific flag bit to confirm that the expected source caused the interrupt.

- process

more on this later

process

- process

- clear flags (if required)

- process

- clear flags (if required)

Some flags need to be cleared explicitly; others will happen as part of normal service.

- process

- clear flags (if required)

Some flags need to be cleared explicitly; others will happen as part of normal service.

Always check whether a flag will be cleared automatically or not.

- process

- clear flags (if required)

- Some flags need to be cleared explicitly; others will happen as part of normal service.

- Always check whether a flag will be cleared automatically or not.

- restore vital registers

# Interrupt Service Routines (continued)

- process

- clear flags (if required)

- Some flags need to be cleared explicitly; others will happen as part of normal service.

- Always check whether a flag will be cleared automatically or not.

- restore vital registers STATUS, BSR, WREG

# Interrupt Service Routines (continued)

- process

- clear flags (if required)

- Some flags need to be cleared explicitly; others will happen as part of normal service.

- Always check whether a flag will be cleared automatically or not.

- restore vital registers STATUS, BSR, WREG

- retfie

- like a subroutine return, but re-enables interrupts

# Example: Timer 0

save vital registers

save vital registersSTATUS, BSR, WREG

- save vital registers STATUS, BSR, WREG

- confirm source

- save vital registersSTATUS, BSR, WREG

- confirm source test TMR0IF in INTCON

- save vital registers STATUS, BSR, WREG

- confirm source test TMR0IF in INTCON

- process

- save vital registers STATUS, BSR, WREG

- confirm source test TMR0IF in INTCON

- process

whatever you need to do

- save vital registers STATUS, BSR, WREG

- confirm source test TMR0IF in INTCON

- process

whatever you need to do

- clear flags (if required)

- save vital registers STATUS, BSR, WREG

- confirm source test TMR0IF in INTCON

- process

whatever you need to do

- clear flags (if required) clear TMR0IF in INTCON

- save vital registersSTATUS, BSR, WREG

- confirm source test TMR0IF in INTCON

- process

whatever you need to do

- clear flags (if required)clear TMR0IF in INTCON

- restore vital registers

- save vital registers STATUS, BSR, WREG

- confirm source test TMR0IF in INTCON

- process

whatever you need to do

- clear flags (if required) clear TMR0IF in INTCON

- restore vital registers STATUS, BSR, WREG

- save vital registersSTATUS, BSR, WREG

- confirm source test TMR0IF in INTCON

- process

whatever you need to do

- clear flags (if required) clear TMR0IF in INTCON

- restore vital registers STATUS, BSR, WREG

- retfie

Interrupts

Introduction Initialization Service Fast register Stack Rules for Interrupts

#### **RETURN** instruction

#### **RETURN** instruction

| RETURN     | Return from Subroutine                                                                                                                                                                                                           |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:    | [label] RETURN [s]                                                                                                                                                                                                               |

| Operands:  | $s \in [0,1]$                                                                                                                                                                                                                    |

| Operation: | $ \begin{split} &(\text{TOS}) \to \text{PC},\\ &\text{if s} = 1\\ &(\text{WS}) \to \text{W},\\ &(\text{STATUSS}) \to \text{STATUS},\\ &(\text{BSRS}) \to \text{BSR},\\ &\text{PCLATU}, \text{PCLATH are unchanged} \end{split} $ |

What does s indicate?

#### **RETFIE** instruction

#### RETFIE instruction

| RETFIE     | Return from Interrupt                                                                                                                       |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:    | [label] RETFIE [s]                                                                                                                          |

| Operands:  | s ∈ [0,1]                                                                                                                                   |

| Operation: | (TOS) → PC,<br>1 → GIE/GIEH or PEIE/GIEL,<br>if s = 1<br>(WS) → W,<br>(STATUSS) → STATUS,<br>(BSRS) → BSR,<br>PCLATU, PCLATH are unchanged. |

Note the difference from a normal RETURN

## Interrupt Resources

The PIC has a set of internal registers to help with interrupt service.

The PIC has a set of internal registers to help with interrupt service.

shadow registers, aka fast register stack

The PIC has a set of internal registers to help with interrupt service.

shadow registers, aka fast register stack

$\rightarrow$  Section 4.7.1, 4.7.5

The PIC has a set of internal registers to help with interrupt service.

shadow registers, aka fast register stack

- $\rightarrow$  Section 4.7.1, 4.7.5

- $\rightarrow$  Section 4.3

The PIC has a set of internal registers to help with interrupt service.

shadow registers, aka fast register stack

- $\rightarrow$  Section 4.7.1, 4.7.5

- $\rightarrow$  Section 4.3

automatically copies STATUS, BSR, WREG when an interrupt occurs

The PIC has a set of internal registers to help with interrupt service.

shadow registers, aka fast register stack

- $\rightarrow$  Section 4.7.1, 4.7.5

- $\rightarrow$  Section 4.3

automatically copies STATUS, BSR, WREG when an interrupt occurs

retfie FAST

The PIC has a set of internal registers to help with interrupt service.

shadow registers, aka fast register stack

- $\rightarrow$  Section 4.7.1, 4.7.5

- $\rightarrow$  Section 4.3

automatically copies STATUS, BSR, WREG when an interrupt occurs

#### retfie FAST

automatically restores STATUS, BSR, WREG on return

The PIC has a set of internal registers to help with interrupt service.

shadow registers, aka fast register stack

- $\rightarrow$  Section 4.7.1, 4.7.5

- $\rightarrow$  Section 4.3

automatically copies STATUS, BSR, WREG when an interrupt occurs

#### retfie FAST

automatically restores STATUS, BSR, WREG on return Why should you only use retfie FAST for high priority interrupts?

#### **RETURN** instruction

#### **RETURN** instruction

| RETURN     | Return from Subroutine                                                                                                                                       |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:    | [label] RETURN [s]                                                                                                                                           |

| Operands:  | $s \in [0,1]$                                                                                                                                                |

| Operation: | $(TOS) \rightarrow PC,$<br>if s = 1<br>$(WS) \rightarrow W,$<br>$(STATUSS) \rightarrow STATUS,$<br>$(BSRS) \rightarrow BSR,$<br>PCLATU, PCLATH are unchanged |

s indicates the FAST option

#### **RETFIE** instruction

#### RETFIE instruction

| RETFIE     | Return from Interrupt                                                                                                                       |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:    | [label] RETFIE [s]                                                                                                                          |

| Operands:  | s ∈ [0,1]                                                                                                                                   |

| Operation: | (TOS) → PC,<br>1 → GIE/GIEH or PEIE/GIEL,<br>if s = 1<br>(WS) → W,<br>(STATUSS) → STATUS,<br>(BSRS) → BSR,<br>PCLATU, PCLATH are unchanged. |

Why does it set GIE/GIEH or PEIE/GIEL?

#### **RETLW** instruction

#### **RETLW** instruction

| RETLW      | Return Literal to W                                                               |

|------------|-----------------------------------------------------------------------------------|

| Syntax:    | [ label ] RETLW k                                                                 |

| Operands:  | $0 \leq k \leq 255$                                                               |

| Operation: | $k \rightarrow W$ ,<br>$(TOS) \rightarrow PC$ ,<br>PCLATU, $PCLATH$ are unchanged |

Why is FAST not an option?

# Rules for Interrupts

# Rules for Interrupts

Never wait in interrupts.

## Rules for Interrupts

Never wait in interrupts.

set flags, have waiting in main program

- Never wait in interrupts.

set flags, have waiting in main program

- On PIC, make timer high priority.

- Never wait in interrupts.

set flags, have waiting in main program

- On PIC, make timer high priority.

see timer overflow code

- Never wait in interrupts.

set flags, have waiting in main program

- On PIC, make timer high priority.

see timer overflow code

- Use interrupts for events of very short duration

- Never wait in interrupts.

set flags, have waiting in main program

- On PIC, make timer high priority.

see timer overflow code

- Use interrupts for events of very short duration i.e. if polling may miss them entirely

Interrupts

Introduction

Initialization

Service

Fast register Stack

Rules for Interrupts

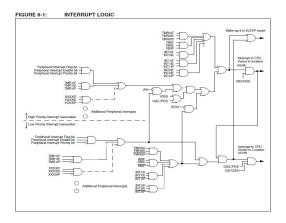

## Interrupt Sources

internal, external

internal, external

$\rightarrow$  Chapter 8 (Figure 8-1)

```

internal, external

→ Chapter 8 (Figure 8-1)

portB, timers, serial, ADC, etc.

```

```

internal, external

```

- $\rightarrow$  Chapter 8 (Figure 8-1)

- $portB,\ timers,\ serial,\ ADC,\ etc.$

- $\rightarrow$  Section 6.5.6

```

internal, external

```

→ Chapter 8 (Figure 8-1)

portB, timers, serial, ADC, etc.

$\rightarrow$  Section 6.5.6

special case: INT0

```

internal, external

```

$\rightarrow$  Chapter 8 (Figure 8-1)

$portB,\ timers,\ serial,\ ADC,\ etc.$

$\rightarrow$  Section 6.5.6

special case: INT0

$\rightarrow$  Section 8.6

Introduction Initialization Service Fast register Stack Rules for Interrupts

# PIC interrupts

## PIC interrupts

Interrupts Se

Introduction

Initialization

Service

Fast register Stack

Rules for Interrupts

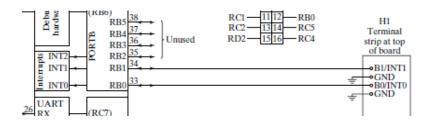

### Qwikflash interrupt connections

### Qwikflash interrupt connections

Introduction

Initialization

Service

Fast register Stack

Rules for Interrupts

# Interrupt Registers

Introduction Initialization Service Fast register Stack Rules for Interrupts

# Interrupt Registers

**RCON**

#### **RCON**

$\rightarrow$  Section 6.4.3

#### **RCON**

$\rightarrow$  Section 6.4.3

INTCON, INTCON2, INTCON3

#### **RCON**

$\rightarrow$  Section 6.4.3

### INTCON, INTCON2, INTCON3

$\rightarrow$  Section 6.4.4

#### **RCON**

$\rightarrow$  Section 6.4.3

INTCON, INTCON2, INTCON3

$\rightarrow$  Section 6.4.4

PIR1, PIR2

#### **RCON**

$\rightarrow$  Section 6.4.3

### INTCON, INTCON2, INTCON3

$\rightarrow$  Section 6.4.4

#### PIR1, PIR2

$\rightarrow$  Section 6.4.5

#### **RCON**

$\rightarrow$  Section 6.4.3

### INTCON, INTCON2, INTCON3

$\rightarrow$  Section 6.4.4

PIR1, PIR2

$\rightarrow$  Section 6.4.5

PIE1, PIE2

#### **RCON**

$\rightarrow$  Section 6.4.3

### INTCON, INTCON2, INTCON3

$\rightarrow$  Section 6.4.4

#### PIR1, PIR2

$\rightarrow$  Section 6.4.5

#### PIE1, PIE2

$\rightarrow$  Section 6.4.6

#### **RCON**

$\rightarrow$  Section 6.4.3

#### INTCON, INTCON2, INTCON3

$\rightarrow$  Section 6.4.4

PIR1, PIR2

$\rightarrow$  Section 6.4.5

PIE1, PIE2

$\rightarrow$  Section 6.4.6

IPR1, IPR2

#### **RCON**

$\rightarrow$  Section 6.4.3

#### INTCON, INTCON2, INTCON3

$\rightarrow$  Section 6.4.4

#### PIR1, PIR2

$\rightarrow$  Section 6.4.5

#### PIE1, PIE2

$\rightarrow$  Section 6.4.6

#### IPR1, IPR2

$\rightarrow$  Section 6.4.7

Interrupts

Introduction Initialization Service Fast register Stack Rules for Interrupts

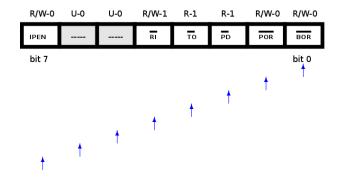

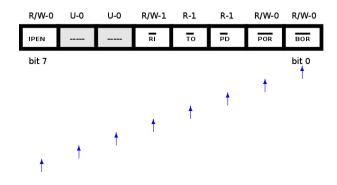

### **RCON**

### **RCON**

### **RCON**

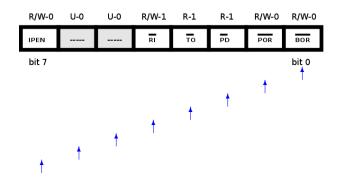

Bits in RCON register

### **RCON**

Bits in RCON register -Set IPEN for priority

Interrupts

Introduction Initialization Service Fast register Stack Rules for Interrupts

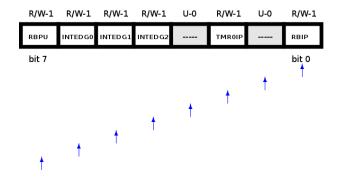

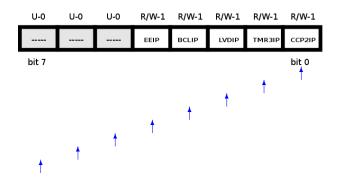

### **INTCON**

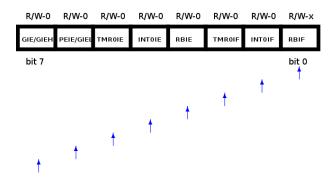

Bits in INTCON register

Bits in INTCON register -Set GIEH to enable high priority, GIEL to enable low priority (if GIEH set)

Interrupts

Introduction Initialization Service Fast register Stack Rules for Interrupts

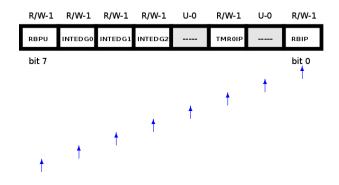

### INTCON2

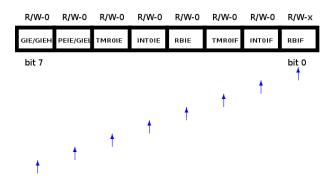

Bits in INTCON2 register

Introduction Initialization Service Fast register Stack Rules for Interrupts

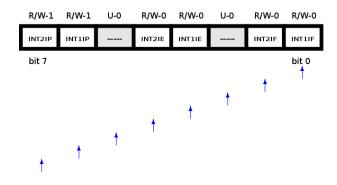

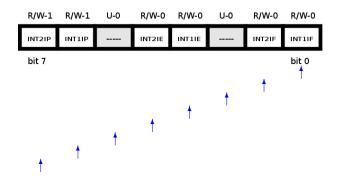

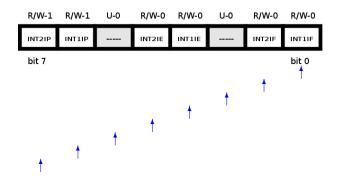

# **INTCON3**

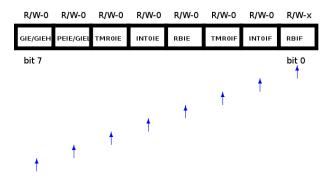

Bits in INTCON3 register

Bits in INTCON3 register -Note INT0 is not mentioned

Introduction Initialization Service Fast register Stack Rules for Interrupts

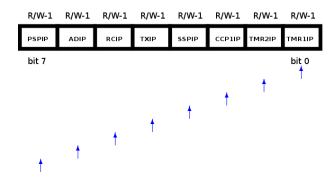

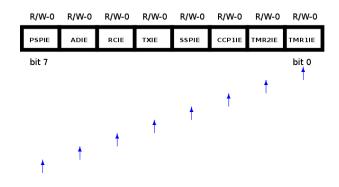

# IPR1

## IPR1

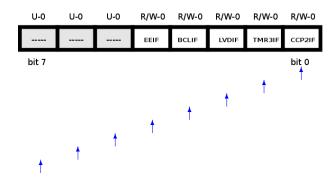

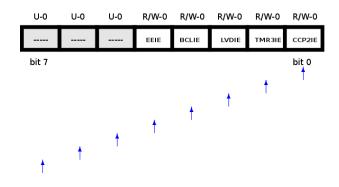

### IPR1

Bits in IPR1 register

Introduction Initialization Service Fast register Stack Rules for Interrupts

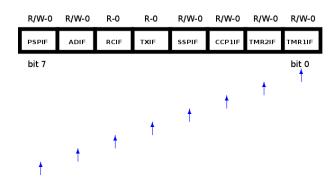

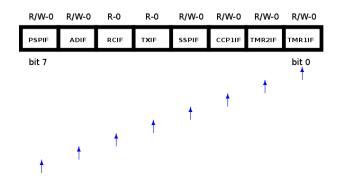

# PIR1

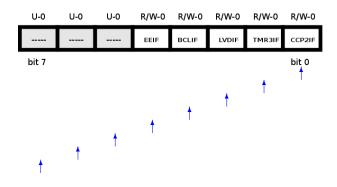

## PIR1

### PIR1

Bits in PIR1 register

Introduction Initialization Service Fast register Stack Rules for Interrupts

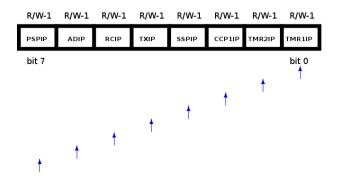

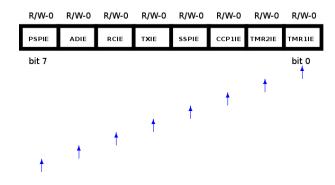

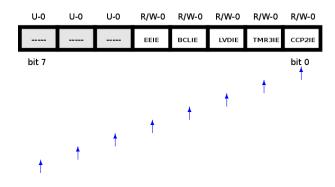

# PIE1

## PIE1

### PIE1

Bits in PIE1 register

Introduction Initialization Service Fast register Stack Rules for Interrupts

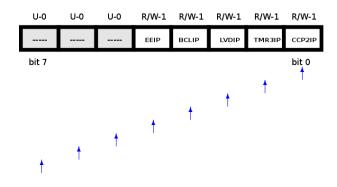

# IPR2

## IPR2

### IPR2

Bits in IPR2 register

Introduction Initialization Service Fast register Stack Rules for Interrupts

# PIR2

## PIR2

### PIR2

Bits in PIR2 register

Introduction Initialization Service Fast register Stack Rules for Interrupts

# PIE2

## PIE2

### PIE2

Bits in PIE2 register