# CP316 Input Capture

Terry Sturtevant

Wilfrid Laurier University

January 28, 2020

Suppose you want to get the time that an event occurs. You could

Suppose you want to get the time that an event occurs. You could

• poll in main loop

Suppose you want to get the time that an event occurs. You could

poll in main loop inaccuracy dependent on length of main loop

Suppose you want to get the time that an event occurs. You could

- poll in main loop inaccuracy dependent on length of main loop

- use an interrupt and read timer in ISR

Suppose you want to get the time that an event occurs. You could

- poll in main loop inaccuracy dependent on length of main loop

- use an interrupt and read timer in ISR delay due to overhead (e.g. context saving) of ISR

Suppose you want to get the time that an event occurs. You could

- poll in main loop inaccuracy dependent on length of main loop

- use an interrupt and read timer in ISR

delay due to overhead (e.g. context saving) of ISR

There is a third option.

## Capture

# Capture

# Capture

Get time when event happens

uses Timer 1

- uses Timer 1

- $\bullet$   $\rightarrow$  Section 16.6

- uses Timer 1

- $\bullet$   $\rightarrow$  Section 16.6

- copies value from timer to input capture register when event occurs

- uses Timer 1

- $\bullet$   $\rightarrow$  Section 16.6

- copies value from timer to input capture register when event occurs

- sets interrupt flag

- uses Timer 1

- $\bullet$   $\rightarrow$  Section 16.6

- copies value from timer to input capture register when event occurs

- sets interrupt flag

## Input capture block

## Input capture block

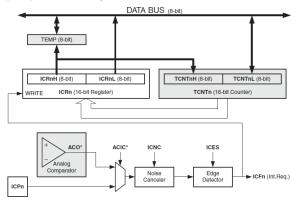

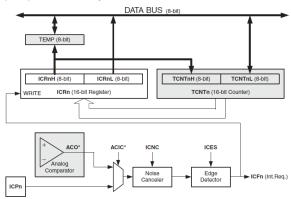

Figure 16-3. Input Capture Unit Block Diagram

## Input capture block

Figure 16-3. Input Capture Unit Block Diagram

Input capture block

## TCCR1B

### TCCR1B

#### 16.11.2 TCCR1B - Timer/Counter1 Control Register B

| Bit           | 7     | 6     | 5 | 4     | 3     | 2    | 1    | 0    |        |

|---------------|-------|-------|---|-------|-------|------|------|------|--------|

| (0x81)        | ICNC1 | ICES1 | - | WGM13 | WGM12 | CS12 | CS11 | CS10 | TCCR1B |

| Read/Write    | R/W   | R/W   | R | R/W   | R/W   | R/W  | R/W  | R/W  |        |

| Initial Value | 0     | 0     | 0 | 0     | 0     | 0    | 0    | 0    |        |

#### • Bit 7 - ICNC1: Input Capture Noise Canceler

Setting this bit (to one) activates the Input Capture Noise Canceler. When the noise canceler is activated, the input from the Input Capture pin (ICP1) is filtered. The filter function requires four successive equal valued samples of the ICP1 pin for changing its output. The Input Capture is therefore delayed by four Oscillator cycles when the noise canceler is enabled.

#### . Bit 6 - ICES1: Input Capture Edge Select

This bit selects which edge on the Input Capture pin (ICP1) that is used to trigger a capture event. When the ICES1 bit is written to zero, a falling (negative) edge is used as trigger, and when the ICES1 bit is written to one, a rising (positive) edge will trigger the capture.

When a capture is triggered according to the ICES1 setting, the counter value is copied into the Input Capture Register (ICR1). The event will also set the Input Capture Flag (ICF1), and this can be used to cause an Input Capture Interrupt. If this Interrupt is enabled.

When the ICR1 is used as TOP value (see description of the WGM13:0 bits located in the TCCR1A and the TCCR1B Register), the ICP1 is disconnected and consequently the Input Capture function is disabled.

### TCCR1B

#### 16.11.2 TCCR1B - Timer/Counter1 Control Register B

| Bit           | 7     | 6     | 5 | 4     | 3     | 2    | 1    | 0    |        |

|---------------|-------|-------|---|-------|-------|------|------|------|--------|

| (0x81)        | ICNC1 | ICES1 | - | WGM13 | WGM12 | CS12 | CS11 | CS10 | TCCR1B |

| Read/Write    | R/W   | R/W   | R | R/W   | R/W   | R/W  | R/W  | R/W  |        |

| Initial Value | 0     | 0     | 0 | 0     | 0     | 0    | 0    | 0    |        |

#### • Bit 7 - ICNC1: Input Capture Noise Canceler

Setting this bit (to one) activates the Input Capture Noise Canceler. When the noise canceler is activated, the input from the Input Capture pin (ICP1) is filtered. The filter function requires four successive equal valued samples of the ICP1 pin for changing its output. The Input Capture is therefore delayed by four Oscillator cycles when the noise canceler is enabled.

#### . Bit 6 - ICES1: Input Capture Edge Select

This bit selects which edge on the Input Capture pin (ICP1) that is used to trigger a capture event. When the ICES1 bit is written to zero, a falling (negative) edge is used as trigger, and when the ICES1 bit is written to one, a rising (positive) edge will trigger the capture.

When a capture is triggered according to the ICES1 setting, the counter value is copied into the Input Capture Register (ICR1). The event will also set the Input Capture Flag (ICF1), and this can be used to cause an Input Capture Interrupt, if this Interrupt is enabled.

When the ICR1 is used as TOP value (see description of the WGM13:0 bits located in the TCCR1A and the TCCR1B Register), the ICP1 is disconnected and consequently the Input Capture function is disabled.

### TCCR1B

### Timer 1 mode selection

### Timer 1 mode selection

Table 16-4. Waveform Generation Mode Bit Description(1)

| Mode | WGM13 | WGM12<br>(CTC1) | WGM11<br>(PWM11) | WGM10<br>(PWM10) | Timer/Counter Mode of<br>Operation  | ТОР    | Update of<br>OCR1x at | TOV1 Flag<br>Set on |

|------|-------|-----------------|------------------|------------------|-------------------------------------|--------|-----------------------|---------------------|

| 0    | 0     | 0               | 0                | 0                | Normal                              | 0xFFFF | Immediate             | MAX                 |

| - 1  | 0     | 0               | 0                | 1                | PWM, Phase Correct, 8-bit           | 0x00FF | TOP                   | воттом              |

| 2    | 0     | 0               | 1                | 0                | PWM, Phase Correct, 9-bit           | 0x01FF | TOP                   | воттом              |

| 3    | 0     | 0               | 1                | 1                | PWM, Phase Correct, 10-bit          | 0x03FF | TOP                   | воттом              |

| 4    | 0     | 1               | 0                | 0                | стс                                 | OCR1A  | Immediate             | MAX                 |

| 5    | 0     | 1               | 0                | 1                | Fast PWM, 8-bit                     | 0x00FF | воттом                | TOP                 |

| 6    | 0     | 1               | 1                | 0                | Fast PWM, 9-bit                     | 0x01FF | воттом                | TOP                 |

| 7    | 0     | 1               | 1                | 1                | Fast PWM, 10-bit                    | 0x03FF | воттом                | TOP                 |

| 8    | 1     | 0               | 0                | 0                | PWM, Phase and Frequency<br>Correct | ICR1   | воттом                | воттом              |

| 9    | 1     | 0               | 0                | 1                | PWM, Phase and Frequency<br>Correct | OCR1A  | воттом                | воттом              |

| 10   | 1     | 0               | 1                | 0                | PWM, Phase Correct                  | ICR1   | TOP                   | воттом              |

| 11   | 1     | 0               | 1                | 1                | PWM, Phase Correct                  | OCR1A  | TOP                   | воттом              |

| 12   | 1     | 1               | 0                | 0                | стс                                 | ICR1   | Immediate             | MAX                 |

| 13   | 1     | 1               | 0                | 1                | (Reserved)                          | -      | -                     | -                   |

| 14   | 1     | 1               | 1                | 0                | Fast PWM                            | ICR1   | воттом                | TOP                 |

| 15   | 1     | 1               | 1                | 1                | Fast PWM                            | OCR1A  | воттом                | TOP                 |

Note: 1. The CTC1 and PWM11:0 bit definition names are obsolete. Use the WGM12:0 definitions. However, the functionality and location of these bits are competible with previous versions of the timer.

### Timer 1 mode selection

Table 16-4. Waveform Generation Mode Bit Description(1)

| Mode | WGM13 | WGM12<br>(CTC1) | WGM11<br>(PWM11) | WGM10<br>(PWM10) | Timer/Counter Mode of<br>Operation  | тор    | Update of<br>OCR1x at | TOV1 Flag<br>Set on |

|------|-------|-----------------|------------------|------------------|-------------------------------------|--------|-----------------------|---------------------|

| 0    | 0     | 0               | 0                | 0                | Normal                              | 0xFFFF | Immediate             | MAX                 |

| 1    | 0     | 0               | 0                | 1                | PWM, Phase Correct, 8-bit           | 0x00FF | TOP                   | воттом              |

| 2    | 0     | 0               | 1                | 0                | PWM, Phase Correct, 9-bit           | 0x01FF | TOP                   | воттом              |

| 3    | 0     | 0               | 1                | 1                | PWM, Phase Correct, 10-bit          | 0x03FF | TOP                   | воттом              |

| 4    | 0     | 1               | 0                | 0                | стс                                 | OCR1A  | Immediate             | MAX                 |

| 5    | 0     | 1               | 0                | 1                | Fast PWM, 8-bit                     | 0x00FF | воттом                | TOP                 |

| 6    | 0     | 1               | 1                | 0                | Fast PWM, 9-bit                     | 0x01FF | воттом                | TOP                 |

| 7    | 0     | 1               | 1                | 1                | Fast PWM, 10-bit                    | 0x03FF | воттом                | TOP                 |

| 8    | 1     | 0               | 0                | 0                | PWM, Phase and Frequency<br>Correct | ICR1   | воттом                | воттом              |

| 9    | 1     | 0               | 0                | 1                | PWM, Phase and Frequency<br>Correct | OCR1A  | воттом                | воттом              |

| 10   | 1     | 0               | 1                | 0                | PWM, Phase Correct                  | ICR1   | TOP                   | воттом              |

| 11   | 1     | 0               | 1                | 1                | PWM, Phase Correct                  | OCR1A  | TOP                   | воттом              |

| 12   | 1     | 1               | 0                | 0                | стс                                 | ICR1   | Immediate             | MAX                 |

| 13   | 1     | 1               | 0                | 1                | (Reserved)                          | -      | -                     | -                   |

| 14   | 1     | 1               | 1                | 0                | Fast PWM                            | ICR1   | воттом                | TOP                 |

| 15   | 1     | 1               | 1                | 1                | Fast PWM                            | OCR1A  | воттом                | TOP                 |

Note: 1. The CTC1 and PWM11:0 bit definition names are obsolete. Use the WGM12:0 definitions. However, the functionality and location of these bits are compatible with previous versions of the timer.

### Timer 1 mode selection

## TIFR1

### TIFR1

#### 16.11.9 TIFR1 - Timer/Counter1 Interrupt Flag Register

| Bit           | 7 | 6 | 5    | 4 | 3 | 2     | 1     | 0    |       |

|---------------|---|---|------|---|---|-------|-------|------|-------|

| 0x16 (0x36)   | _ | - | ICF1 | - | - | OCF1B | OCF1A | TOV1 | TIFR1 |

| Read/Write    | R | R | R/W  | R | R | R/W   | R/W   | R/W  |       |

| Initial Value | 0 | 0 | 0    | 0 | 0 | 0     | 0     | 0    |       |

#### · Bit 7, 6 - Reserved

These bits are unused bits in the ATmega48A/PA/88A/PA/168A/PA/328/P, and will always read as zero.

#### • Bit 5 - ICF1: Timer/Counter1, Input Capture Flag

This flag is set when a capture event occurs on the ICP1 pin. When the Input Capture Register (ICR1) is set by the WGM13:0 to be used as the TOP value, the ICF1 Flag is set when the counter reaches the TOP value. ICF1 is automatically cleared when the Input Capture Interrupt Vector is executed. Alternatively, ICF1 can be cleared by writing a logic one to its bit location.

### TIFR1

#### 16.11.9 TIFR1 - Timer/Counter1 Interrupt Flag Register

| Bit           | 7 | 6 | 5    | 4 | 3 | 2     | 1     | 0    |       |

|---------------|---|---|------|---|---|-------|-------|------|-------|

| 0x16 (0x36)   | - | - | ICF1 | - | - | OCF1B | OCF1A | TOV1 | TIFR1 |

| Read/Write    | R | R | R/W  | R | R | R/W   | R/W   | R/W  | •     |

| Initial Value | 0 | 0 | 0    | 0 | 0 | 0     | 0     | 0    |       |

#### · Bit 7, 6 - Reserved

These bits are unused bits in the ATmega48A/PA/88A/PA/168A/PA/328/P, and will always read as zero.

#### . Bit 5 - ICF1: Timer/Counter1, Input Capture Flag

This flag is set when a capture event occurs on the ICP1 pin. When the Input Capture Register (ICR1) is set by the WGM13.0 to be used as the TOP value, the ICP1 Flag is set when the counter reaches the TOP value. ICP1 is automatically cleared when the Input Capture Interrupt Vector is executed. Alternatively, ICP1 can be cleared by writing a logic one to its bit location.

#### TIFR1

## TIMSK1

### TIMSK1

#### 16.11.8 TIMSK1 - Timer/Counter1 Interrupt Mask Register

#### · Bit 7, 6 - Reserved

These bits are unused bits in the ATmega48A/PA/88A/PA/168A/PA/328/P, and will always read as zero.

#### Bit 5 - ICIE1: Timer/Counter1, Input Capture Interrupt Enable

When this bit is written to one, and the I-flag in the Status Register is set (interrupts globally enabled), the "Imer/Counter! Input Capture interrupt is enabled. The corresponding interrupt Vector (see "Interrupts" on page 57) is executed when the ICF1 Flag, located in TiFR1, is set.

### TIMSK1

#### 16.11.8 TIMSK1 - Timer/Counter1 Interrupt Mask Register

#### · Bit 7, 6 - Reserved

These bits are unused bits in the ATmega48A/PA/88A/PA/168A/PA/328/P, and will always read as zero.

#### . Bit 5 - ICIE1: Timer/Counter1, Input Capture Interrupt Enable

When this bit is written to one, and the I-flag in the Status Register is set (interrupts globally enabled), the "Immer/Counter1 Input Capture interrupt is enabled. The corresponding Interrupt Vector (see "Interrupts" on page 57) is executed when the ICF1 Flag, located in TiFR1, is set.

### TIMSK1

• interrupt allows saved value to be copied elsewhere

- interrupt allows saved value to be copied elsewhere

- 16 bit value must be read LOW, then HIGH